# Personal Communications

IC Handbook

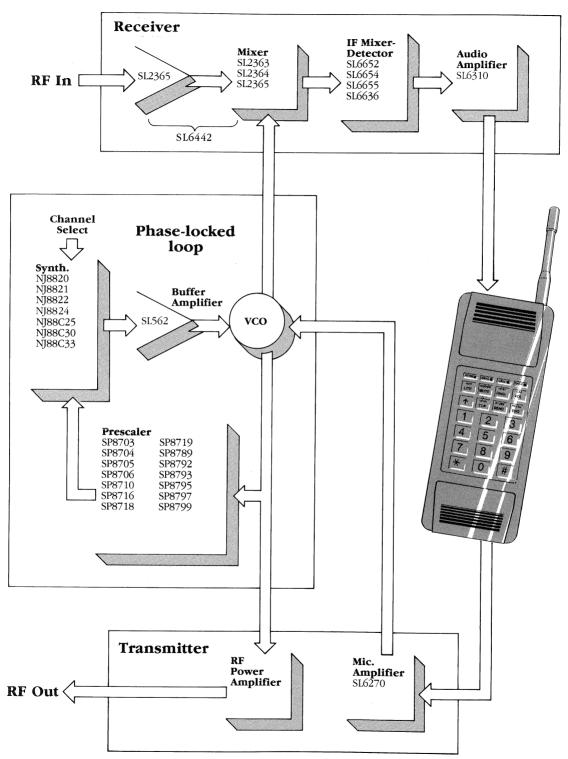

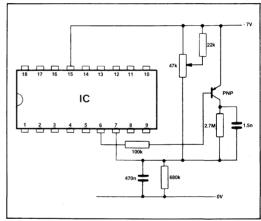

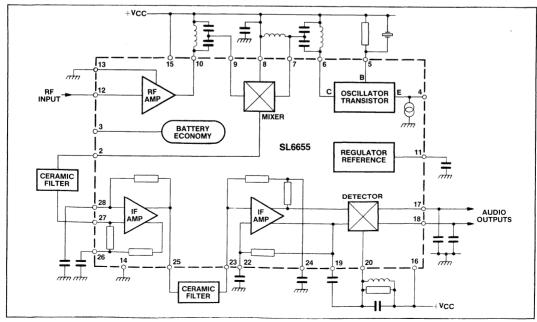

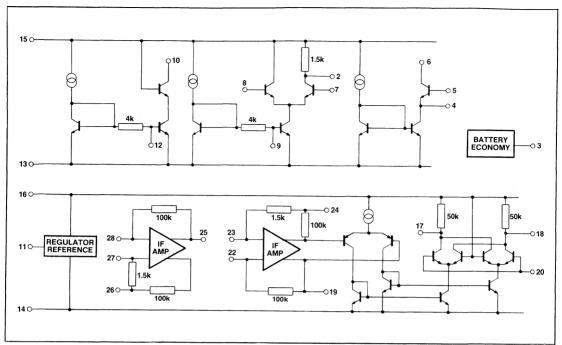

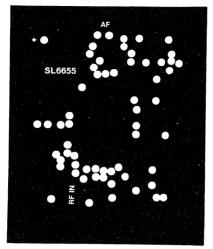

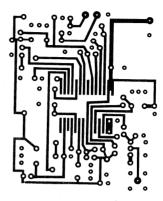

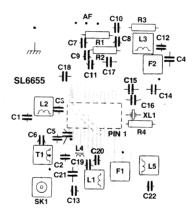

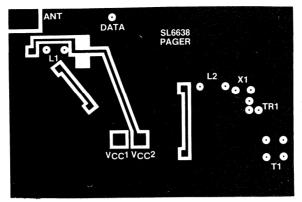

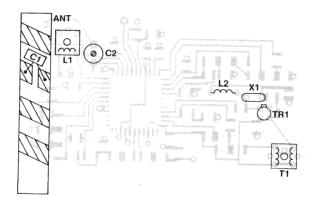

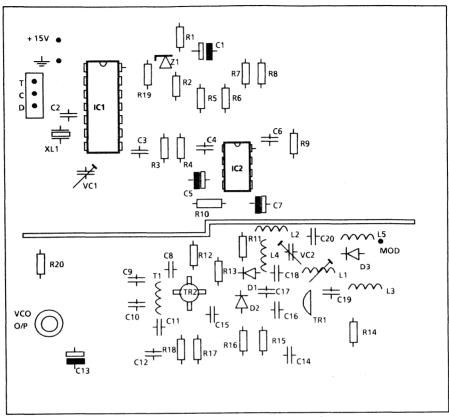

Plessey products in a typical hand held radio.

# PERSONAL COMMUNICATIONS

IC Handbook

# **Foreword**

Plessey Semiconductors has created a range of products specific to applications in the growing market for hand-held radio-communications.

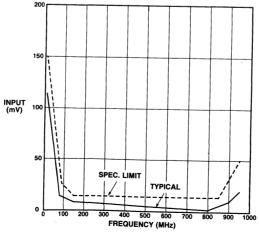

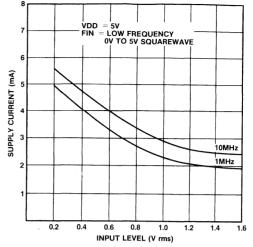

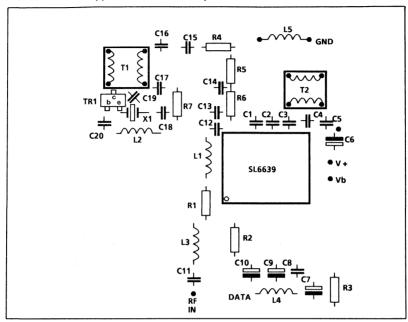

The features which identify ICs as being suitable for this market area are *supply current* and *frequency*. Since battery life is all-important in hand-held equipment, every effort is made by our IC designers to develop products which require the absolute minimum current. New ICs such as the SL6639 pager chip and SP8705 (a programmable multi-modulus divider, which consumes only 5mA at 1000MHz) exemplify this philosophy.

New frequency band allocations have now been made in the 450 and 900MHz regions for pagers, cordless telephones and cellular radios. Plessey's bipolar processes have been developed to operate at these and even higher frequencies for dividers, IF amplifiers and single chip synthesisers. The 1.4-Micron CMOS process is also capable of operating at high frequencies and the latest generation of CMOS synthesisers are included in this handbook.

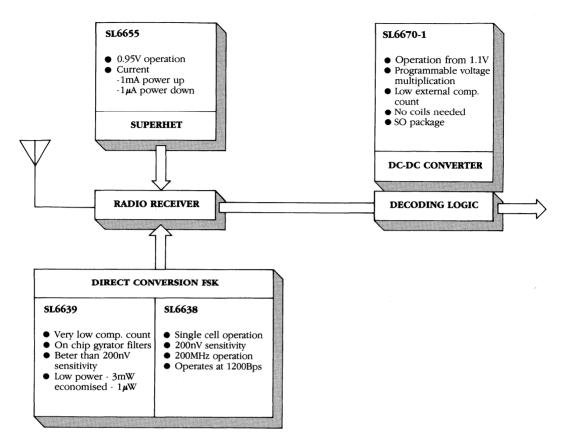

Also making its debut is a range of new low power FM receivers. Suited for use in paging, the new ICs offer ideal solutions for Direct Conversion or Superhet front ends.

All the relevant Plessey ICs can be supplied in surface mount miniature plastic and some in plastic quad packages in order to satisfy the requirement for small size in compact hand-held radio equipment.

Finally, the Quality Assurance Procedures that are applied to other Plessey Semiconductor products (from consumer electronics to Defence projects) are applied to radio-communications ICs with equal rigour. Performance and long term reliability are thereby guaranteed in what can be a demanding operating environment.

# **Contents**

|                                             | Page |

|---------------------------------------------|------|

| Foreword                                    | 2    |

| Product index - by application              | 5    |

| Product index - by circuit type             | 7    |

| Product list                                | 9    |

| Semi-custom design                          | 10   |

| The quality concept                         | 16   |

| Technical data                              | 19   |

| Application notes:                          |      |

| SL2365 applications                         | 197  |

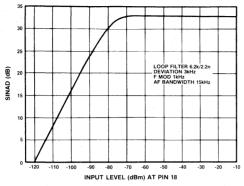

| Loop filter design                          | 199  |

| A serially-programmable VHF frequency       |      |

| synthesiser                                 | 211  |

| Phase noise intermodulation and             |      |

| dynamic range                               | 213  |

| Design compromises in single loop           |      |

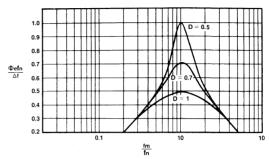

| frequency synthesisers                      | 222  |

| SL6638 direct conversion paging receiver    |      |

| applications                                | 229  |

| The care and feeding of high speed dividers | 238  |

| SL6140 tuned amplifier application          | 244  |

| SL6639 demonstration board                  | 246  |

| NJ88C30 VHF frequency synthesiser           | 247  |

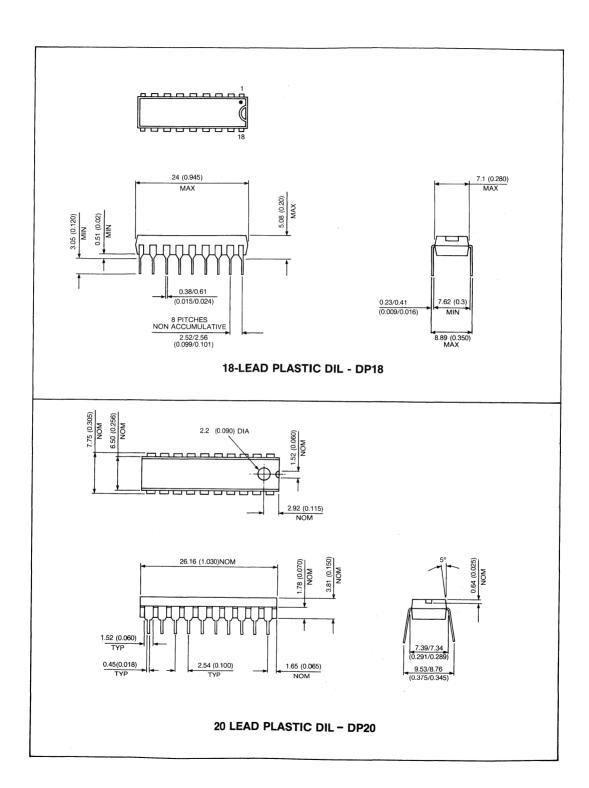

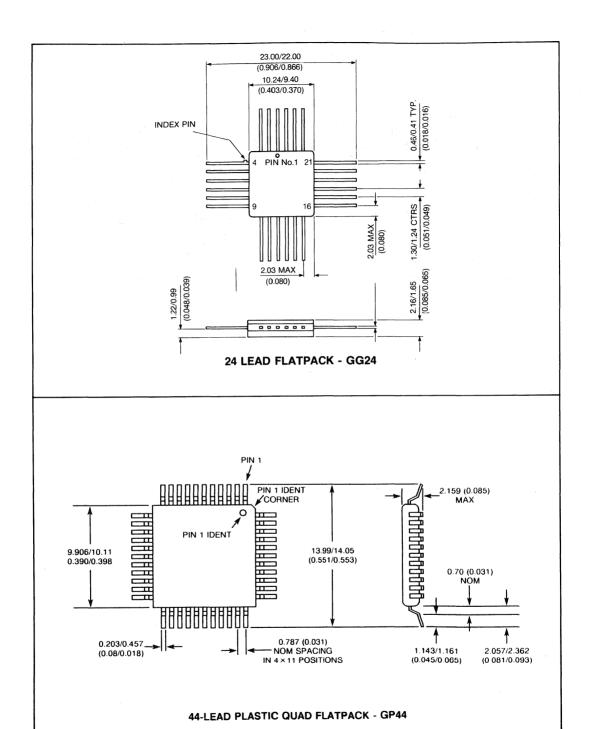

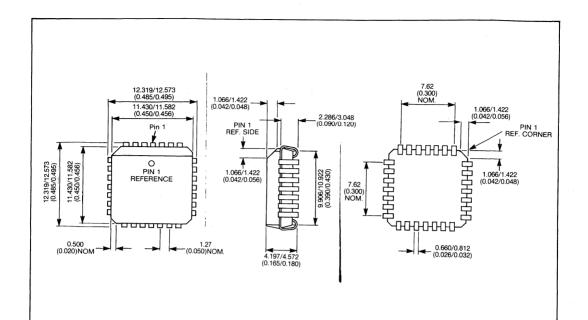

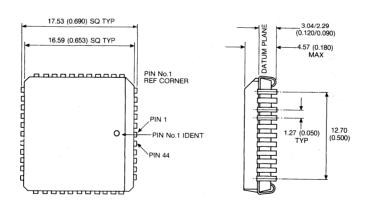

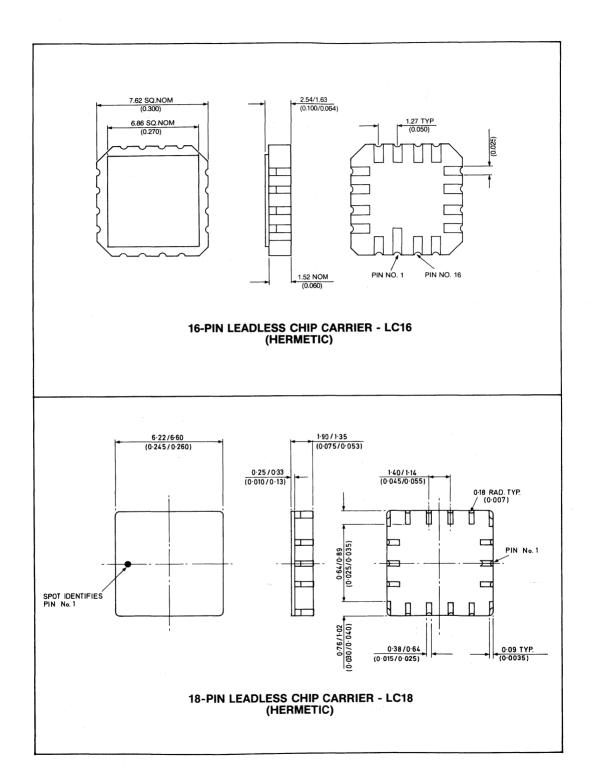

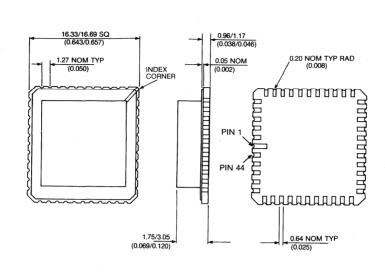

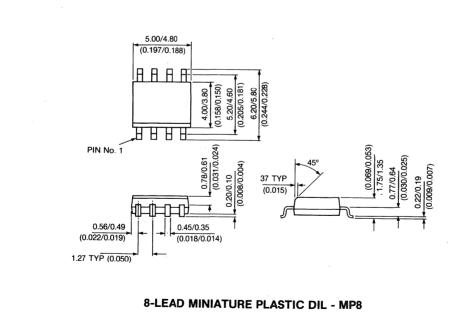

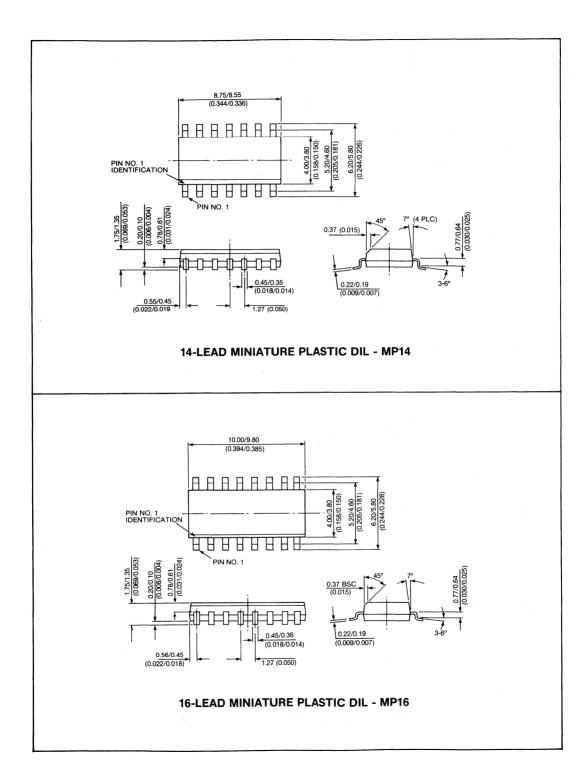

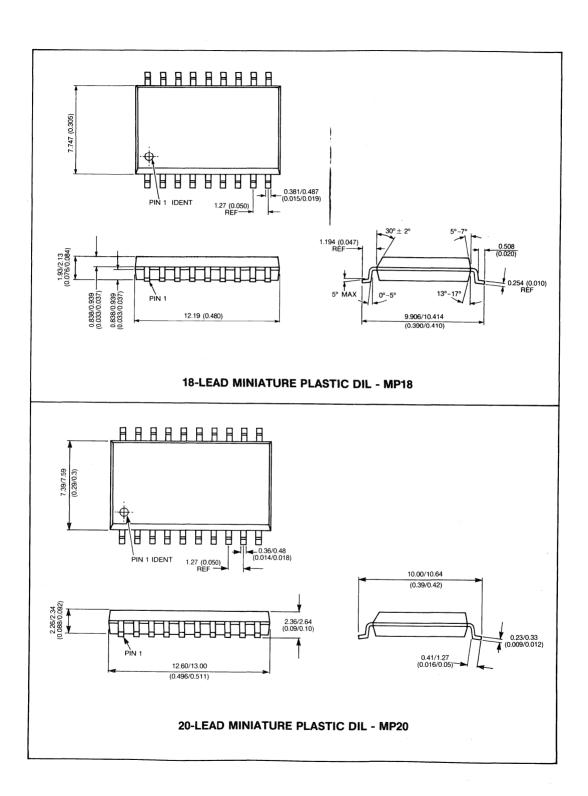

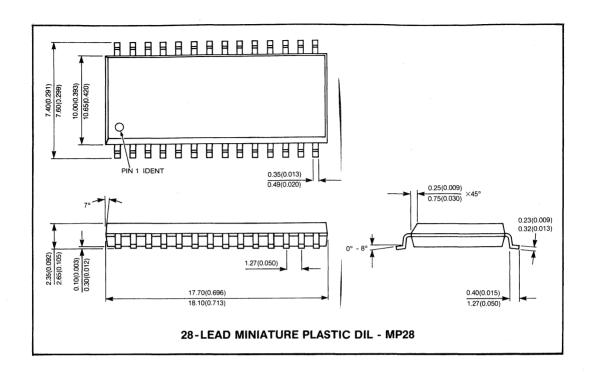

| Package outlines                            | 251  |

| Stop press                                  | 267  |

| Plessey Semiconductors locations            | 287  |

The Plessey pager solution

# Product index - by application

#### **Dividers**

| Ratio   | Frequency<br>(MHz) | Supply<br>Current<br>(mA,max) | Supply<br>Voltage<br>(V) | Type No. | Page |

|---------|--------------------|-------------------------------|--------------------------|----------|------|

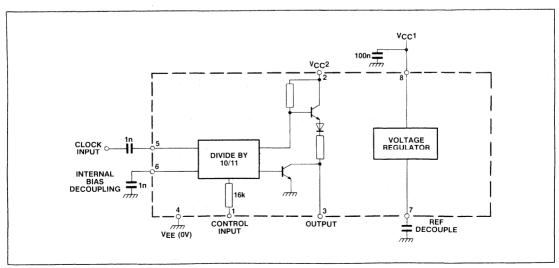

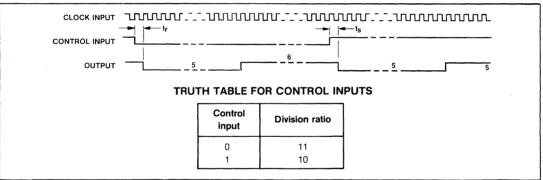

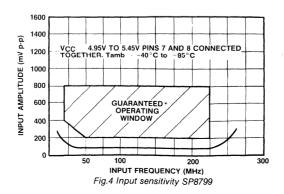

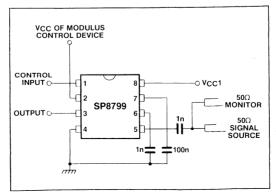

| 10/11   | 225                | 7                             | 5.2 or 6.8 to 9.5        | SP8799   | 141  |

| 20/21   | 225                | 7                             | 5.2 or 6.8 to 9.5        | SP8789   | 129  |

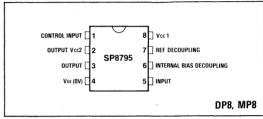

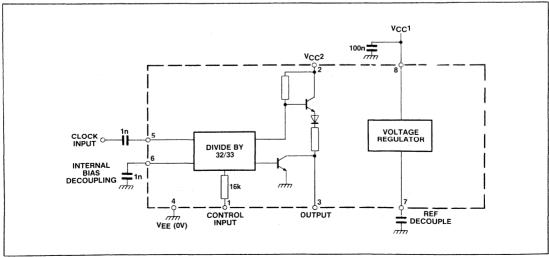

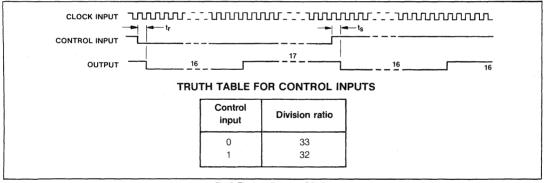

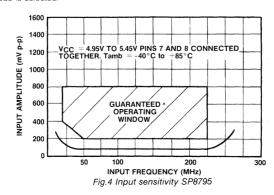

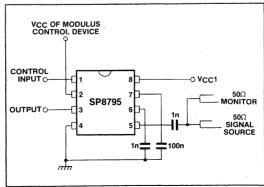

| 32/33   | 225                | 7                             | 5.2 or 6.8 to 9.5        | SP8795   | 135  |

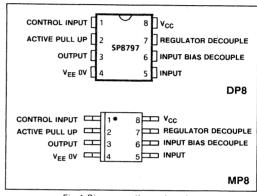

| 32/33   | 225                | 7.8                           | 4.5 to 9.5               | SP8797   | 138  |

| 40/41   | 225                | 7                             | 5.2 or 6.8 to 9.5        | SP8793   | 132  |

| 40/41   | 520                | 10.5                          | 5.2                      | SP8716   | 126  |

| 64/65   | 950                | 10                            | 3 to 5                   | SP8704   | 117  |

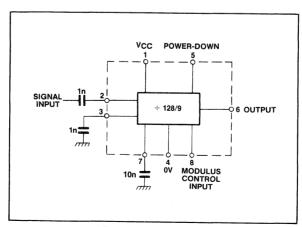

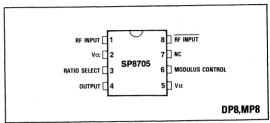

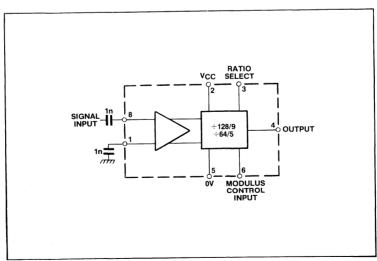

| 64/65   | 1100               | 5                             | 3 to 5                   | SP8705   | 119  |

| 64/65   | 520                | 10.5                          | 5.2                      | SP8718   | 126  |

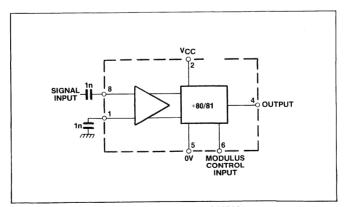

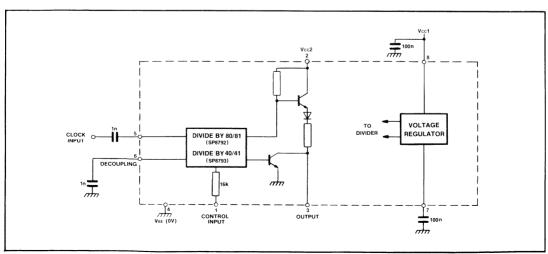

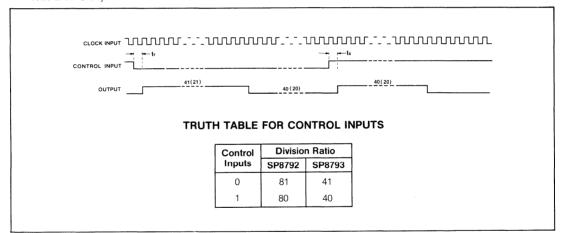

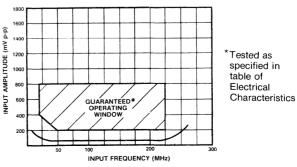

| 80/81   | 225                | 7                             | 5.2 or 6.8 to 9.5        | SP8792   | 132  |

| 80/81   | 520                | 10.5                          | 5.2                      | SP8719   | 126  |

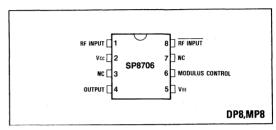

| 80/81   | 1000               | 10                            | 3 to 5                   | SP8706   | 121  |

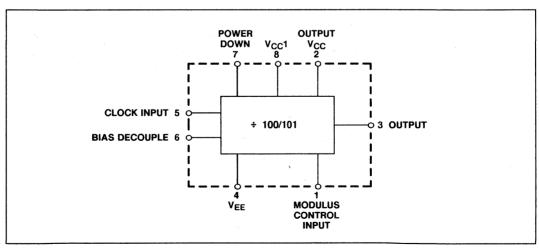

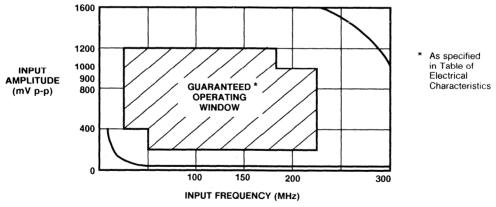

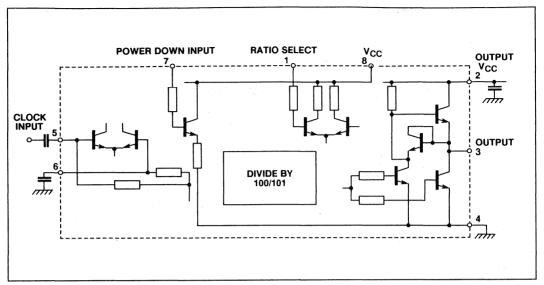

| 100/101 | 225                | 8.5                           | 3 to 10                  | SP8710B  | 123  |

| 128/129 | 950                | 10                            | 3 to 5                   | SP8704   | 117  |

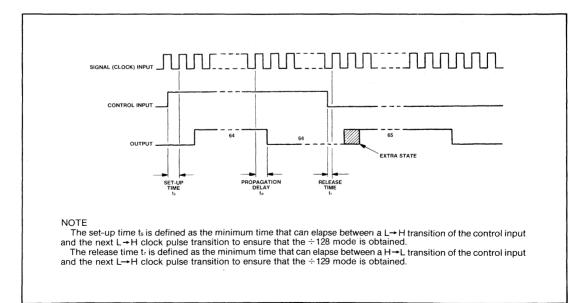

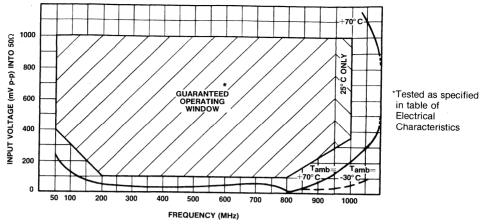

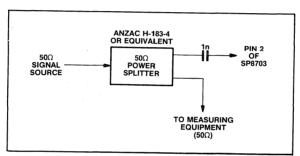

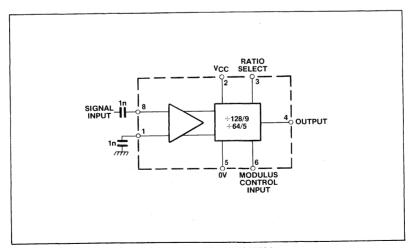

| 128/129 | 1000               | 30                            | 5                        | SP8703   | 114  |

| 128/129 | 1100               | 5                             | 3 to 5                   | SP8705   | 119  |

#### **Synthesisers**

| Input Frequency<br>(MHz) | Supply<br>Current<br>(mA) | Supply<br>Voltage<br>(V) | Type No. | Page |

|--------------------------|---------------------------|--------------------------|----------|------|

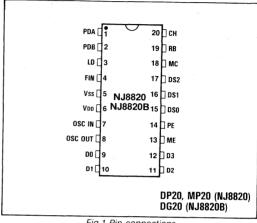

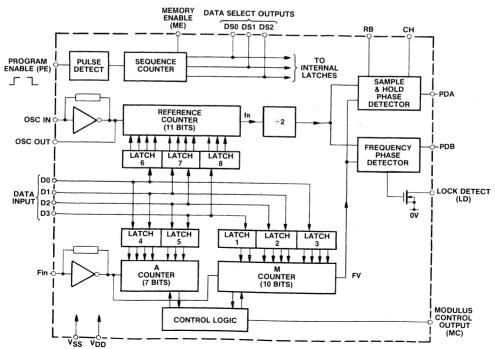

| 10                       | 3.5                       | 5                        | NJ8820/B | 144  |

| 10                       | 3.5                       | 5                        | NJ8820GG | 151  |

| 10                       | 3.5                       | 5                        | NJ8821GG | 162  |

| 10                       | 6.3                       | 5                        | NJ8822/B | 167  |

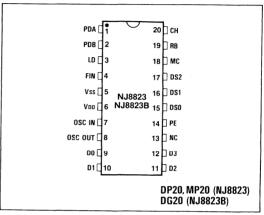

| 10                       | 3.5                       | 5                        | NJ8823/B | 172  |

| 10                       | 6.3                       | 5                        | NJ8824/B | 177  |

| 20                       |                           | 3 to 5                   | NJ88C25  | 182  |

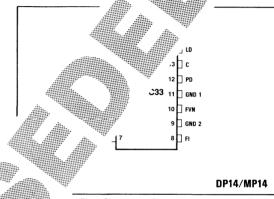

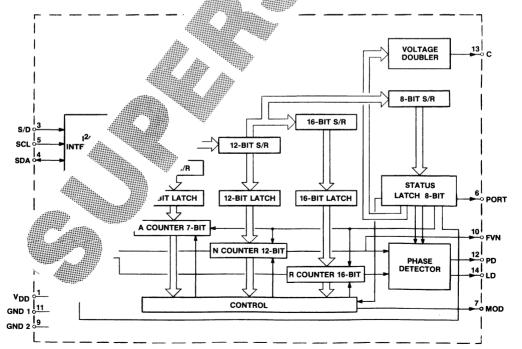

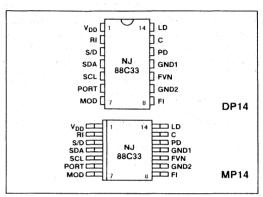

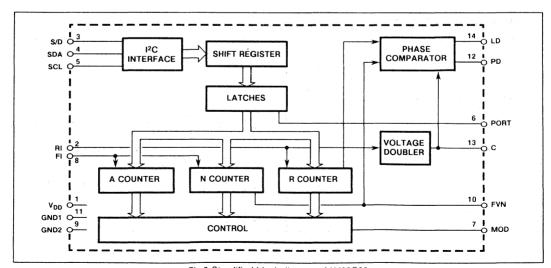

| 100                      | 4                         | 3 to 5                   | NJ88C33  | 269  |

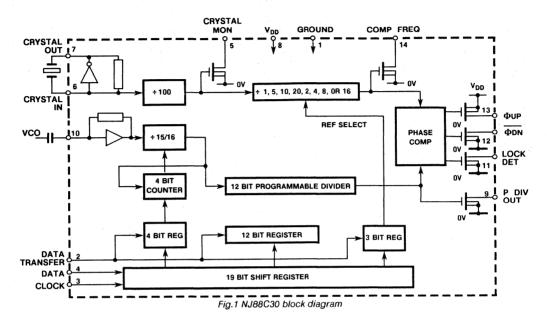

| 200                      | 4                         | 5                        | NJ88C30  | 188  |

#### IF Amplifiers/Detectors

| Input Frequency<br>(MHz) | Supply<br>Current<br>(mA) | Supply<br>Voltage<br>(V) | Туре No.            | Page |

|--------------------------|---------------------------|--------------------------|---------------------|------|

| 100                      | 1.5                       | 2.5 to 7.5               | SL66521             | 77   |

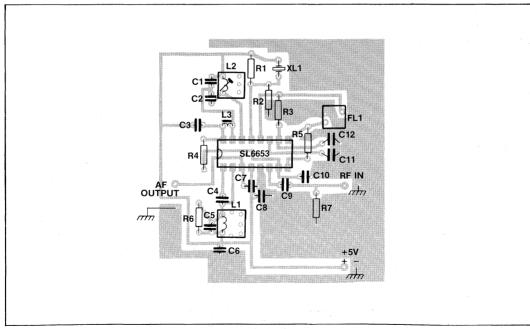

| 100                      | 1.5                       | 2.5 to 7.5               | SL6653 <sup>2</sup> | 85   |

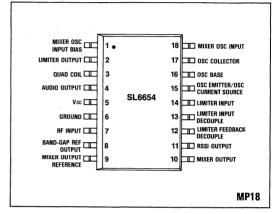

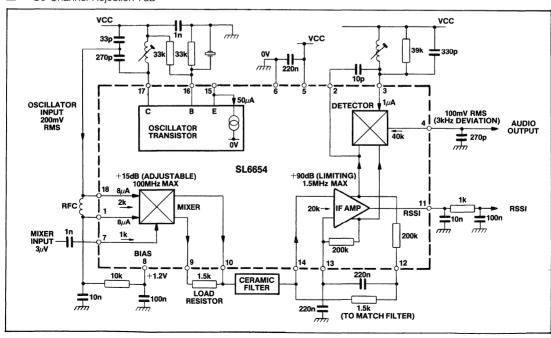

| 100                      | 1.5                       | 2.5 to 7.5               | SL66543             | 90   |

<sup>1.</sup> With RSSI output and differential audio outputs. 2. Single audio output, no RSSI.

<sup>3.</sup> RSSI output, single audio output.

#### Low Power Radio Receivers (Pagers)

| Input Frequency | Supply<br>Current<br>(mA) | Supply<br>Voltage<br>(V) | Type No. | Page |

|-----------------|---------------------------|--------------------------|----------|------|

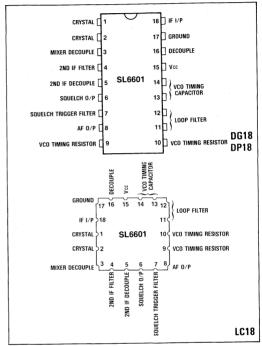

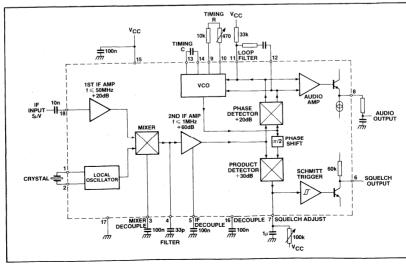

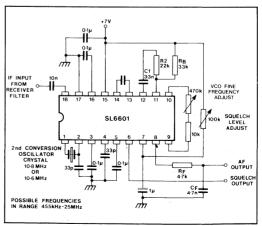

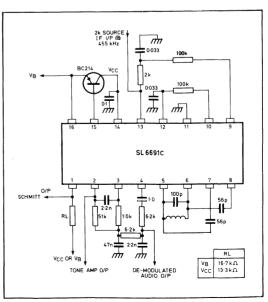

| 455kHz          | 2.3                       | 7                        | SL6601C  | 47   |

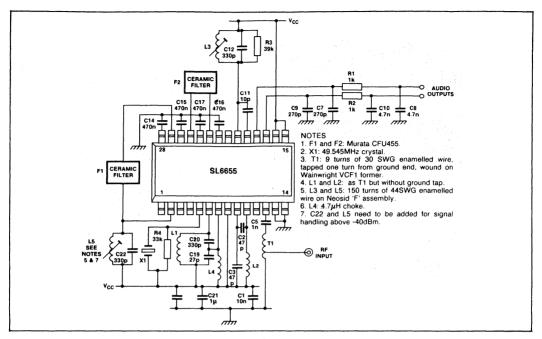

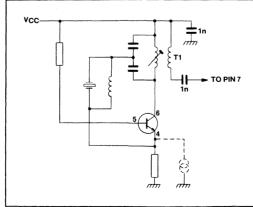

| 100MHz          | 1.0                       | 0.95 to 5                | SL6655   | 96   |

| 200MHz          | 2.5                       | 0.9 to 3.5               | SL66371  | 60   |

| 200MHz          | 2                         | 0.9 to 3.5               | SL6638   | 61   |

| 200MHz          | 2                         | 0.9 to 3.5               | SL6639   | 70   |

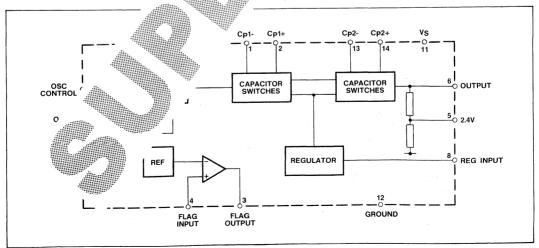

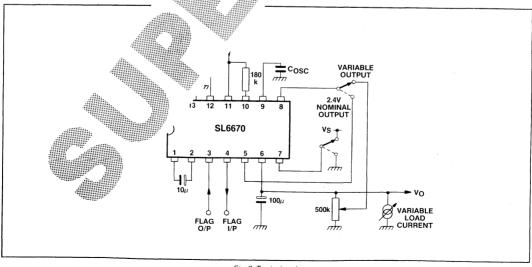

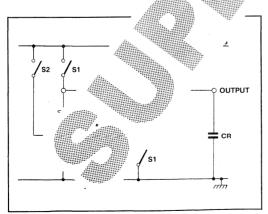

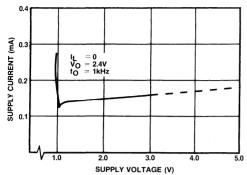

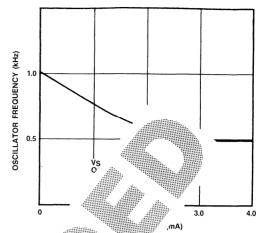

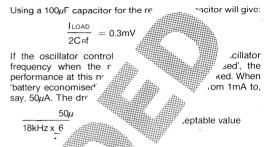

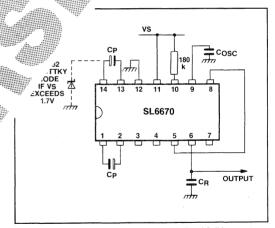

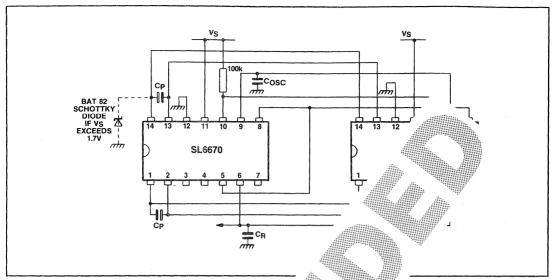

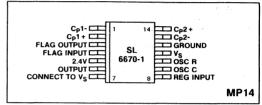

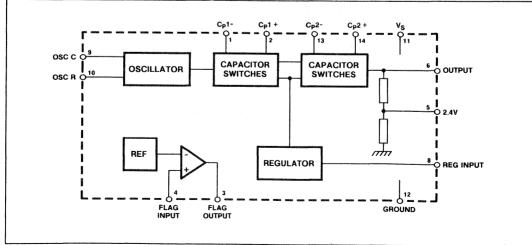

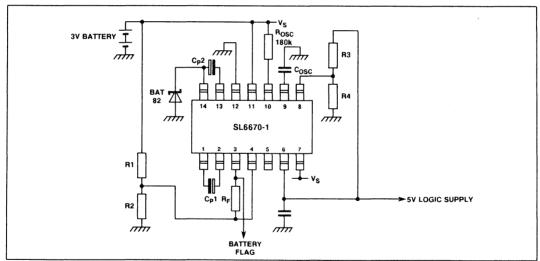

| N/A             | 0.25                      | 1.1 to 5                 | SL6670-1 | 279  |

| 455kHz          |                           | 6                        | SL6691C  | 111  |

<sup>1.</sup> Not recommended for new designs; use SL6638 or SL6639.

#### Cordless Telephones

| Input Frequency<br>(MHz) | Supply<br>Current<br>(mA) | Supply<br>Voltage<br>(V) | Type No. | Page |

|--------------------------|---------------------------|--------------------------|----------|------|

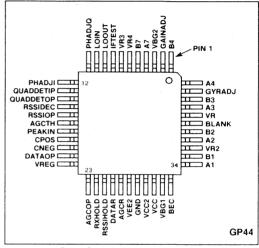

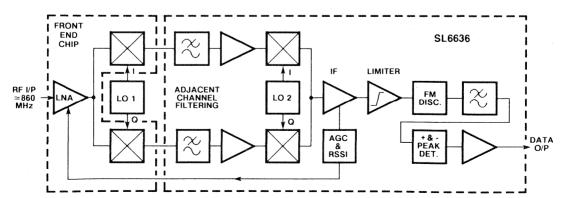

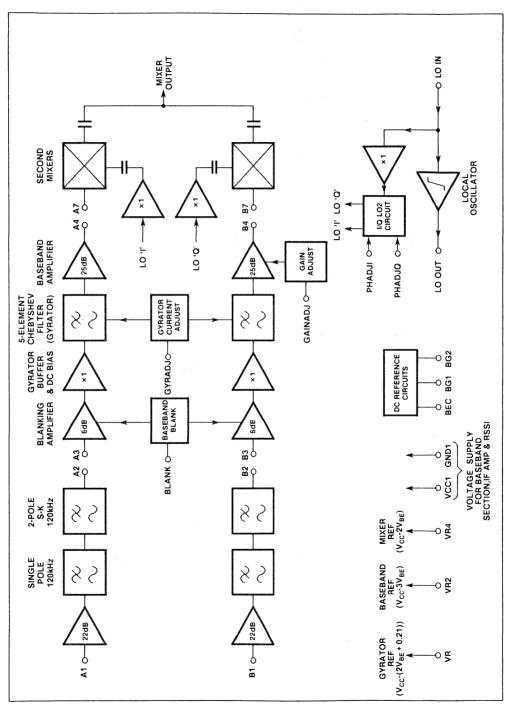

| N/A                      | 4.5                       | 5                        | SL6636   | 53   |

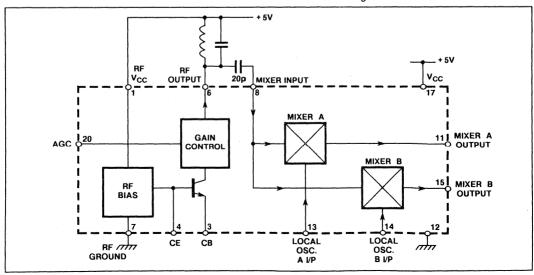

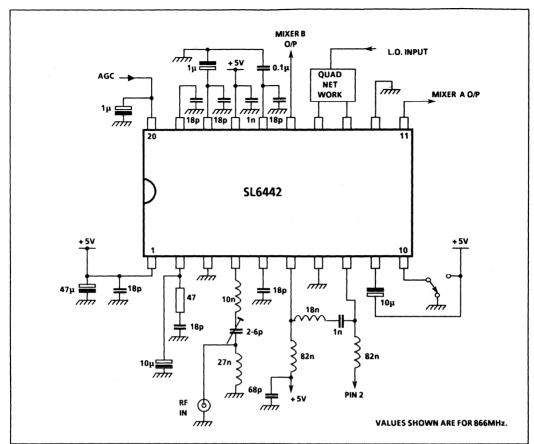

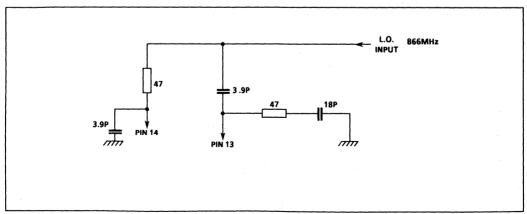

| 1000                     | 4.1                       | 4.5 to 6.5               | SL6442   | 43   |

#### **UHF** Transistor Arrays

| f⊤<br>(GHz) |  | Supply<br>Current<br>(mA) | Supply<br>Voltage<br>(V) | Type No.            | Page |

|-------------|--|---------------------------|--------------------------|---------------------|------|

| 5           |  | 4                         | 2.0                      | SL2363C & SL2364C1  | 29   |

| 5           |  | 4                         | 2.0                      | SL2365 <sup>2</sup> | 31   |

<sup>1. 2</sup> long-tailed pairs with tail transistors. 2. Two long tailed pairs with current mirrors.

#### **Amplifiers**

| Function                | Supply<br>Current | Supply<br>Voltage<br>(V) | Type No. | Page |

|-------------------------|-------------------|--------------------------|----------|------|

| Audio                   | 7.5mA             | 4.5 to 13                | SL6310C  | 40   |

| Microphone              | 10mA              | 4.5 to 10                | SL6270   | 37   |

| Op-amp                  | 20mA              | $\pm$ 1.5 to $\pm$ 10    | SL562    | 26   |

| 300MHz low noise amplif | ier 40μΑ¹         | 2 to 5                   | SL560C   | 21   |

# Product index - by circuit type (contd.)

#### **Amplifiers**

| Type No. | Supply<br>Voltage<br>(V) | Supply<br>Current | Bandwidth     | Maximum<br>Offset<br>Voltage (mV) | Gain<br>(dB) | Page |

|----------|--------------------------|-------------------|---------------|-----------------------------------|--------------|------|

| SL560C1  | 2 to 15V                 | 20mA              | 300MHz        | . 132 (1) 141<br>=                | 35           | 21   |

| SL5621   | ±1.5 to +10              | 20µA to 5mA       | 50kHz to 4MHz | 5                                 | 95           | 26   |

| SL6310C  | 4.5 to 15V               | 15mA              | 1MHz          | 20                                | 50           | 40   |

<sup>1.</sup> Noise figure 20nV/√Hz (Guaranteed)

#### Matched Transistors and Arrays

| Type No.             | LV co | :o(V)<br>Typ. | Iсм(mA) | Typ.Cut-off<br>Frequency<br>(GHz) | No. of<br>Transistors | h <sub>FE</sub><br>(Ic = 1mA)<br>(Min.) | Page |

|----------------------|-------|---------------|---------|-----------------------------------|-----------------------|-----------------------------------------|------|

| SL2363C1             | 6     | 9             | 12      | 5.0                               | 6                     | 20                                      | 29   |

| SL2364C <sup>2</sup> | 6     | 9             | 12      | 5.0                               | 6                     | 20                                      | 29   |

| SL2365 <sup>3</sup>  | 6     | 9             | 12      | 5.0                               | 8                     | 20                                      | 31   |

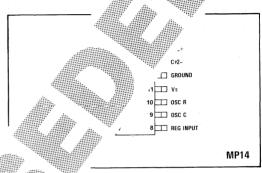

<sup>1.</sup> TO-5 package (CM10) 2. DIL package (DC14,DP14). 3. Plastic DIL surface mount package (MP14).

#### Radiocoms

| Type No. | Function                                                           | Page |

|----------|--------------------------------------------------------------------|------|

| SL6270C  | Microphone amplifier with AGC                                      | 37   |

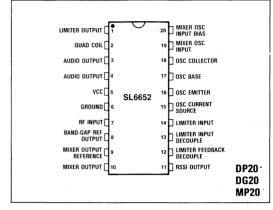

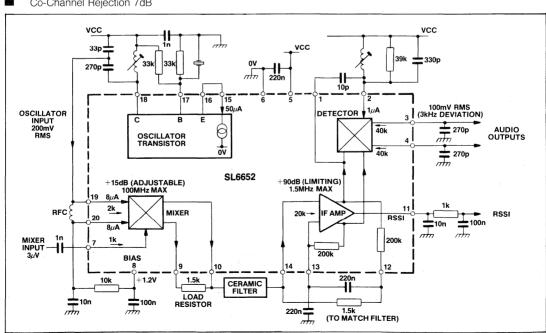

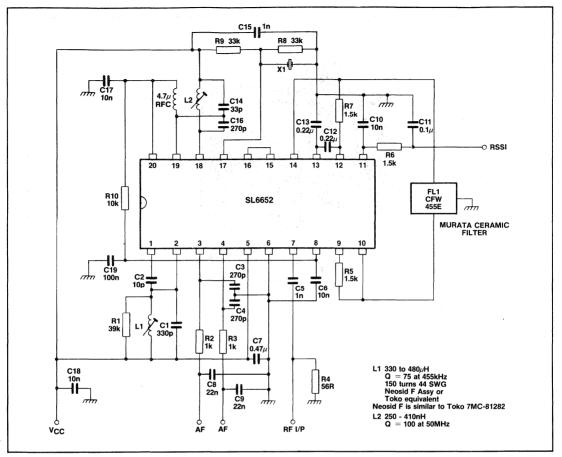

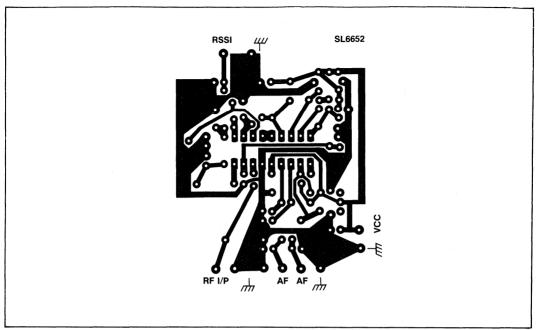

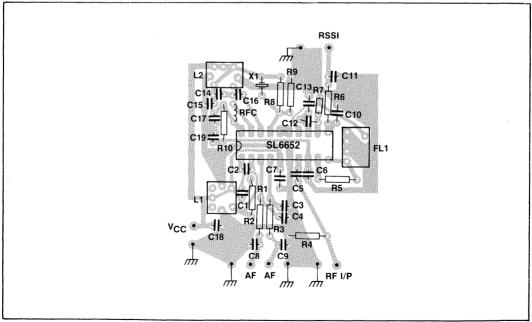

| SL6652   | FM IF and quadrature detector with RSSI and differential audio O/P | 77   |

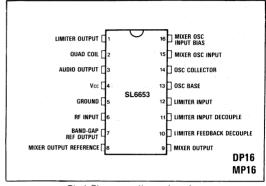

| SL6653   | FM IF and quadrature detector                                      | 85   |

| SL6654   | FM IF and quadrature detector with RSSI                            | 90   |

#### Low Power Radio Receivers (Pagers)

| Type No. | Function                                                         | Page |

|----------|------------------------------------------------------------------|------|

| SL6601C  | FM IF, PLL detector (double conversion) and RF mixer             | 47   |

| SL6637   | Direct conversion FSK receiver - not recommended for new designs | 60   |

| SL6638   | Direct conversion FSK receiver                                   | 61   |

| SL6639   | Direct conversion FSK receiver with on chip filter               | 70   |

| SL6655   | Superhet receiver consuming 1mA at 0.95V                         | 96   |

| SL6670-1 | Low power voltage multiplier (inverter)                          | 279  |

| SL6691C  | FM IF and detector (455kHz only)                                 | 111  |

#### Cordless Telephones

| Type No. | Function                                   | Page |

|----------|--------------------------------------------|------|

| SL6636   | Baseband receiver chip                     | 53   |

| SL6442   | RF front end low noise amp with two mixers | 43   |

#### SP8000 Series Variable Modulus Dividers - Bipolar

| Type No. | Function                | Supply Current<br>(Typ.)<br>(mA) | Page |

|----------|-------------------------|----------------------------------|------|

| SP8703   | 1GHz ÷ 128/129          | 20                               | 114  |

| SP8704   | 950MHz ÷ 128/129 64/65  | 10                               | 117  |

| SP8705   | 1100MHz ÷ 128/129 64/65 | 4                                | 119  |

| SP8706   | 950MHz ÷ 80/81          | 10                               | 121  |

| SP8710   | 225MHz ÷ 100/101        | 7                                | 123  |

| SP8716   | 520MHz ÷ 40/41          | 7                                | 126  |

| SP8718   | 520MHz ÷ 64/65          | 7                                | 126  |

| SP8719   | 520MHz ÷ 82/81          | 7                                | 126  |

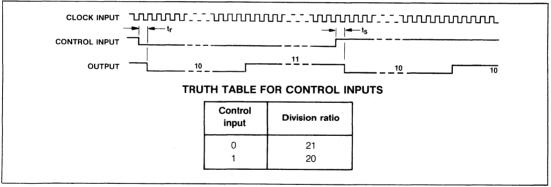

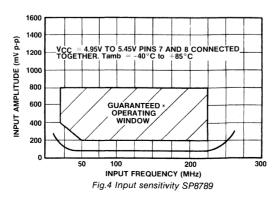

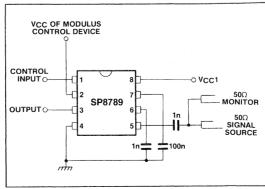

| SP8789   | 225MHz ÷ 20/21          | 4                                | 129  |

| SP8792   | 225MHz ÷ 80/81          | 4                                | 132  |

| SP8793   | 225MHz ÷ 40/41          | 4                                | 132  |

| SP8795   | 225MHz ÷ 32/33          | 4                                | 135  |

| SP8797   | 225MHz ÷ 32/33          |                                  | 138  |

| SP8799   | 225MHz ÷ 10/11          | 4                                | 141  |

#### Radio Synthesisers

| Type No. | Function                                                                            | Page |

|----------|-------------------------------------------------------------------------------------|------|

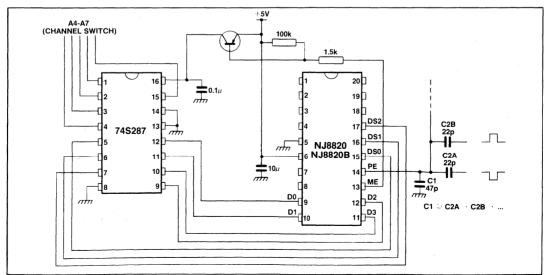

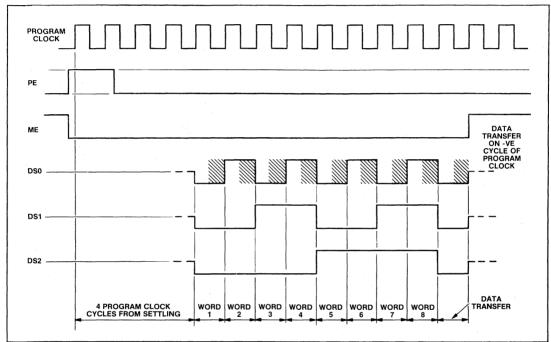

| NJ8820/B | CMOS control circuit with PROM interface                                            | 144  |

| NJ8820GG | Flatpack version of NJ8820                                                          | 151  |

| NJ8821/B | CMOS control circuit with microprocessor parallel interface and resettable counters | 157  |

| NJ8821GG | Flatpack version of NJ8821                                                          | 162  |

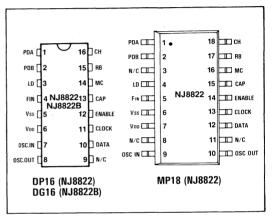

| NJ8822/B | CMOS control circuit with microprocessor serial interface and resettable counters   | 167  |

| NJ8823/B | As NJ8821 with zero reset removed                                                   | 172  |

| NJ8824/B | As NJ8822 with zero reset removed                                                   | 177  |

| NJ88C25  | 3V control circuit with microprocessor serial interface                             | 182  |

| NJ88C30  | 200MHz single chip synthesiser for General Application                              | 188  |

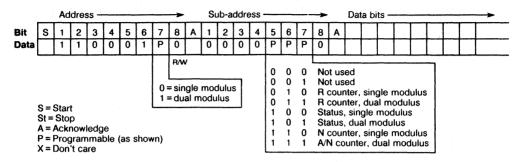

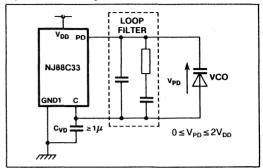

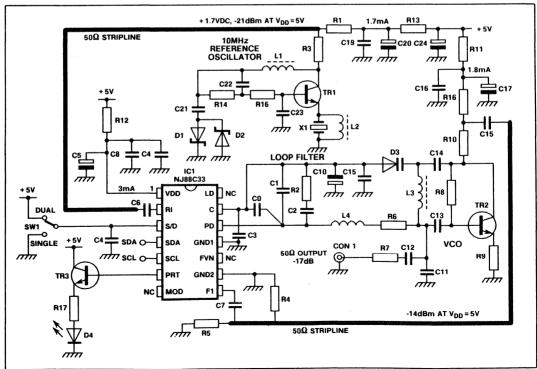

| NJ88C33  | I <sup>2</sup> C interface 120MHz single chip synthesiser                           | 269  |

Purchase of Plessey Semiconductors' I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patents Rights to use these components in I<sup>2</sup>C systems, provided that the systems conform to the I<sup>2</sup>C Standard Specification as defined by Philips.

# Product list - alpha numeric

| TYPE No. | DESCRIPTION                                                    | PAGE |

|----------|----------------------------------------------------------------|------|

| SL560C   | 300MHz low noise amplifier                                     | 21   |

| SL562    | Low noise programmable op-amp                                  | 26   |

| SL2363C  | Very high performance transistor array                         | 29   |

| SL2364C  | Very high performance transistor array                         | 29   |

| SL2365   | Very high performance transistor array                         | 31   |

| SL6140   | 400MHz wideband AGC amplifier                                  | 32   |

| SL6270C  | Gain controlled pre-amplifier                                  | 37   |

| SL6310C  | Switchable audio amplifier                                     | 40   |

| SL6442   | 1GHz amplifier/mixer                                           | 43   |

| SL6601C  | FM IF, PLL detector (double conversion) and RF mixer           | 47   |

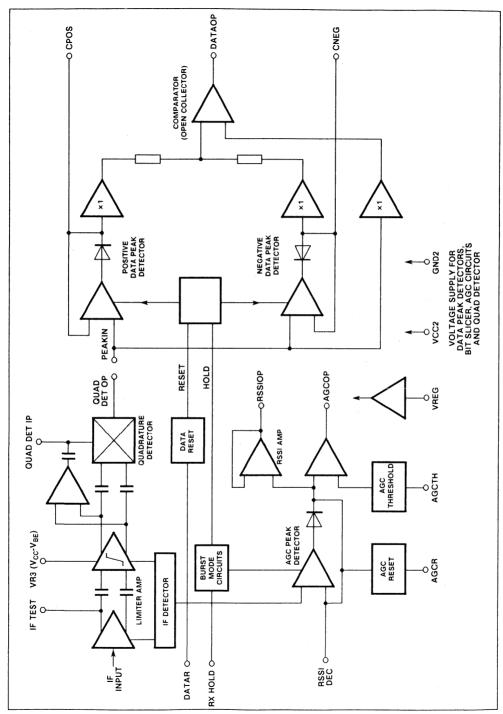

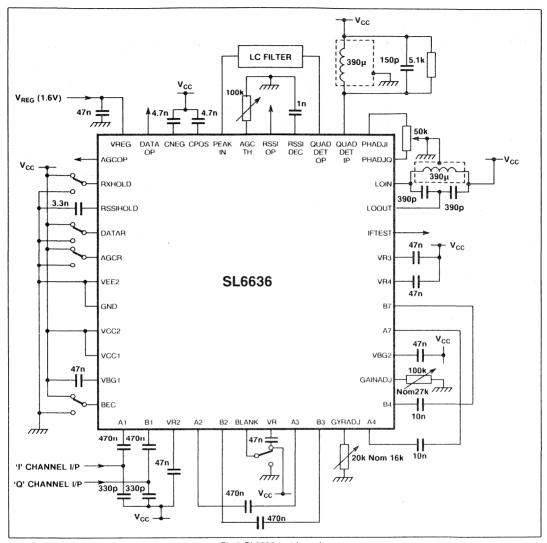

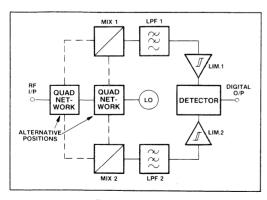

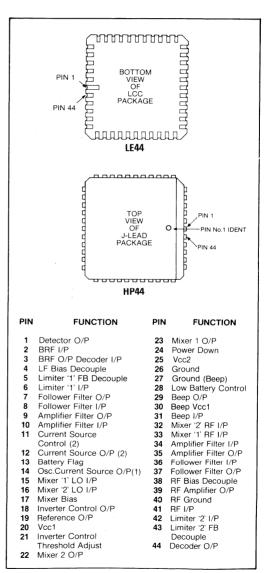

| SL6636   | Low power baseband demodulator for digital cordless telephones | 53   |

| SL6637   | Direct conversion FSK receiver                                 | 60   |

| SL6638   | 200MHz direct conversion FSK data receiver                     | 61   |

| SL6639   | 200MHz direct conversion FSK data receiver                     | 70   |

| SL6652   | Low power IF/AF circuit for FM cellular radio                  | 77   |

| SL6653   | Low power IF/AF circuit for FM receivers                       | 85   |

| SL6654   | Low power IF/AF circuit for FM cellular radio                  | 90   |

| SL6655   | Superhet receiver                                              | 96   |

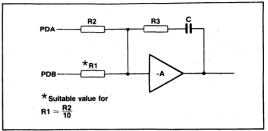

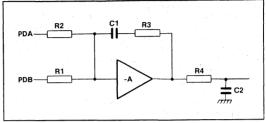

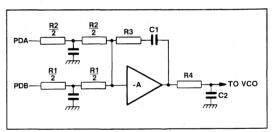

| SL6670-1 | 1.1V DC/DC voltage converter                                   | 279  |

| SL6691C  | IF system paging receivers                                     | 111  |

| SP8703   | 1GHz low current divide by 128/129                             | 114  |

| SP8704   | 950MHz very low current divide by 128/129 or 64/65             | 117  |

| SP8705   | 1100MHz very low current divide by 128/129 or 64/65            | 119  |

| SP8706   | 950MHz very low current two-modulus divider                    | 121  |

| SP8710B  | 225MHz low power two-modulus divide by 100/101                 | 123  |

| SP8716   | 520MHz divide by 40/41                                         | 126  |

| SP8718   | 520MHz divide by 64/65                                         | 126  |

| SP8719   | 520MHz divide by 80/81                                         | 126  |

| SP8789   | 225MHz divide by 20/21                                         | 129  |

| SP8792   | 225MHz divide by 80/81                                         | 132  |

| SP8793   | 225MHz divide by 40/41                                         | 132  |

| SP8795   | 225MHz divide by 32/33                                         | 135  |

| SP8797   | 225MHz divide by 32/33                                         | 138  |

| SP8799   | 225MHz divide by 10/11                                         | 141  |

| NJ8820/B | Frequency synthesiser (PROM interface)                         | 144  |

| NJ8820GG | Flatpack version of NJ8820                                     | 151  |

| NJ8821/B | Frequency synthesiser (Microprocessor interface)               | 157  |

| NJ8821GG | Flatpack version of NJ8821                                     | 162  |

| NJ8822/B | Frequency synthesiser (Microprocessor serial interface)        | 167  |

| NJ8823/B | Frequency synthesiser (Microprocessor serial interface)        | 172  |

| NJ8824/B | Frequency synthesiser (Microprocessor serial interface)        | 177  |

| NJ88C25  | Frequency synthesiser at 3V (Microprocessor serial interface)  | 182  |

| NJ88C30  | Single chip VHF synthesiser                                    | 188  |

| NJ88C33  | Single chip I <sup>2</sup> C synthesiser                       | 269  |

# Semi-Custom design

#### CMOS gate arrays

#### CLA SERIES

The CLA 5000 family is a  $2\mu m$ , 40 MHz, double layer metal CMOS product. There are 9 arrays ranging from 640 to 10044 gates.

Like all of our CMOS, the  $2\mu m$  arrays use stacked vias over contacts, routing through cells

|            |                  |                |            | - 100 |

|------------|------------------|----------------|------------|-------|

| ARRAY TYPE | MAXIMUM<br>GATES | MAXIMUM<br>I/O | POWER PINS |       |

| CLA 51XX   | 640              | 36             | 4          |       |

| CLA 52XX   | 1232             | 48             | 8          |       |

| CLA 53XX   | 2016             | 64             | 8          |       |

| CLA 54XX   | 3060             | 80             | 8          |       |

| CLA 55XX   | 4408             | 96             | 16         |       |

| CLA 56XX   | 5984             | 112            | 16         |       |

| CLA 57XX   | 7104             | 128            | 16         |       |

| CLA 58XX   | 8064             | 144            | 16         |       |

| CLA 59XX   | 10044            | 160            | 16         |       |

|            |                  |                |            |       |

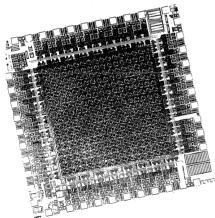

#### CLA 60000 1.4 $\mu$ m CMOS Channelless Arrays

New to the Plessey Semiconductors gate array family is the 1.5µm CMOS "CHANNELLESS ARRAY".

The "CHANNELLESS ARRAY" technique combines the advantages of gate arrays with the full layout flexibility of cell based designs.

| ARRAY TYPE | <b>MAXIMUM GATES</b> | TOTAL PADS |

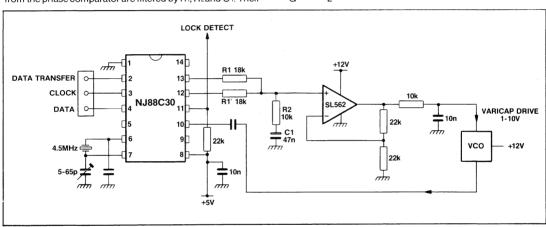

|------------|----------------------|------------|

| CLA 61XXX  | 2040                 | 40         |

| CLA 62XXX  | 5488                 | 64         |

| CLA 63XXX  | 10608                | 88         |

| CLA 64XXX  | 19928                | 120        |

| CLA 65XXX  | 35784                | 160        |

| CLA 66XXX  | 55616                | 200        |

| CLA 67XXX  | 80560                | 240        |

| CLA 68XXX  | 110112               | 256        |

#### CLA 5000 Features

- 2μm CMOS, DLM process

- 1.2 ns (typ), 2 input gate delay

- 40 MHz clock frequency

- 160 I/Os with TTL/CMOS compatibility

- Intrinsic latch-up immunity and over-voltage protection

- 3V to 5.5V operating range

- Full military spec (-55 to 125°C)

- 5μW/Gate/MHz power consumption

In the corners of each gate array, special circuit configurations have been included. A power-on reset circuit, crystal oscillator maintaining circuit, performance monitor and a bandgap reference circuit are currently available.

High density RAM and ROM configuration can also be programmed onto the arrays.

#### CLA 60000 Features

- 1.4µm CMOS, DLM process

- All pads may be programmed as Input, Output, I/O or Power

- 700 ps (typ), 2-input gate delay

- 5.5µW/Gate/MHz power consumption

- 70 MHz clock frequency

- 5 volt full military specification (-55 to 125°C)

- Analog functions available (op amp, comparator)

#### Bipolar gate arrays

Il ULA products are designed to provide cost-effective solutions to a wide range of applications.

The DS series of bipolar digital arrays feature fast internal gates and differential logic functions for superior speed/power performance. These provide predictable and closely matched delays for system speeds of 100MHz at complexities to 10,000 gates. Easy interfacing to ECL, TTL and CMOS logic is combined with on-chip analog functions such as oscillators, comparators, schmitt triggers and operational amplifiers.

#### DS' SERIES

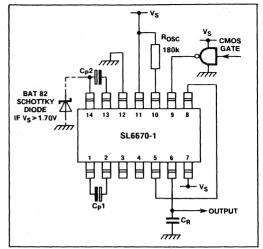

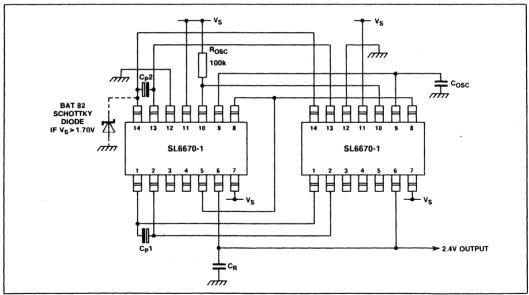

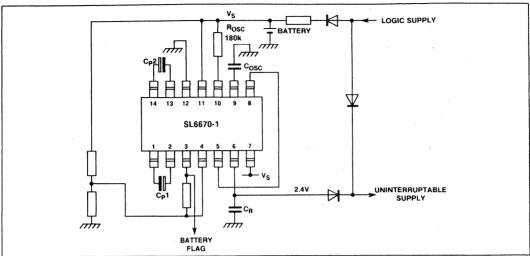

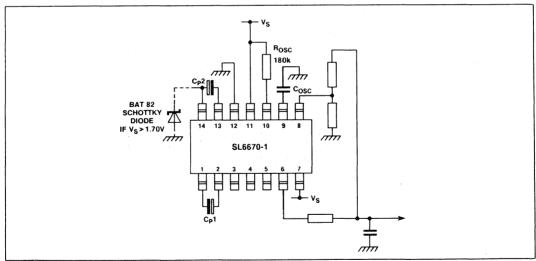

#### HIGH SPEED DIGITAL ARRAYS WITH HIGH PERFORMANCE ANALOG

| ARRAY<br>TYPE | EQUIVALENT<br>GATE<br>COUNT | PERIPHERAL<br>I/O CELLS | BOND<br>PADS |

|---------------|-----------------------------|-------------------------|--------------|

| ULA 6DS       | 630                         | 32                      | 40           |

| ULA 12DS      | 1210                        | 44                      | 52           |

| ULA 19DS      | 1870                        | 64                      | 72           |

| ULA 25DS      | 2550                        | 74                      | 82           |

| ULA 32DS      | 3230                        | 82                      | 92           |

| ULA 38DS      | 3990                        | 90                      | 100          |

| ULA 47DS      | 4860                        | 104                     | 114          |

| ULA 60DS      | 6210                        | 122                     | 132          |

| ULA 80DS      | 7920                        | 138                     | 150          |

| ULA 100DS     | 10000                       | 138                     | 150          |

#### DIGITAL ARRAYS WITH ANALOG FUNCTIONS

#### ULA DS series

- 100 MHz system speed

- Omplexities to 10,000 gates

- 1.5 micron DLM process

- High performance analog functions on chip

- Good asynchronous performance

- Flexible interface capability

- Differential logic for superior speed/power product

- Closely matched components

- Silicon compilers

48mA output drive per peripheral cell

- Digital & linear macros

- Comprehensive CAD support

- Range of speed/power options

- Full military operation

#### Bipolar analog/digital arrays

DF series arrays feature enhanced analog capabilities alongside the logic gates from the DS

series. The 37 high performance linear components in each analog cell – and there are up to 58 cells – are designed to guarantee close matching and low offsets. These are optimised for

producing 100MHz VCOs or crystal oscillators together with precision AGC amplifiers featuring 60MHz bandwidths. Comparators offering 10ns delay and only 1mV offsets are complemented by precision monostables with 20ns periods accurate to 500ps. These features make the DF series ideally suited to a wide range of applications such as data recovery in the computer peripherals and telecommunications fields

#### **ULA DF series**

- 100MHz digital system speed

- 100MHz analog capability

- Close matching cell components

- Low offsets

- Digital and analog macros

- Complexities to 2000 gates

- Speed/power options

- Differential logic

- On chip bandgap reference

- 50mA drive capability

- Fully CAD supported

- Silicon compilers

- 1.5 micron feature size

- Full military operation

#### **DA Series Features**

- Combines complex analog and digital circuitry on a single chip

- NPN & PNP transistors allowing comprehensive analog designs

- Operation from 1 to 18 volt supply

- High current drive capability (120mA)

- Two gate switching speed options

- Fully supported customer design routeExtensive range of analog and

- logic macros

- Proven hard analog macros in silicon

- Auto place and route

Rapid physical turnaround to silicon

- Available to commercial, industrial & military requirements

## 'DF' SERIES HIGH SPEED DIGITAL WITH ENHANCED ANALOG FUNCTIONS

| ARRAY<br>TYPE | EQUIVALENT<br>GATE<br>COUNT | ANALOG<br>CELLS | BOND<br>PADS |

|---------------|-----------------------------|-----------------|--------------|

| ULA 5DF       | 560                         | 32              | 43           |

| ULA 11DF      | 1100                        | 44              | 55           |

| ULA 14DF      | 1430                        | 54              | 65           |

| ULA 18DF      | 1725                        | 58              | 69           |

| 'DA' SERIES   |                             |                 |              |

| 2 DA          | 20                          | 6               | 18           |

| 8 DA          | 80                          | 10              | 22           |

| 18 DA         | 176                         | 14              | 26           |

| 25 DA         | 256                         | 18              | 30           |

| 35 DA         | 352                         | 18              | 34           |

| 50 DA         | 512                         | 22              | 36           |

| 90 DA         | 924                         | 32              | 44           |

| 150 DA        | 1428                        | 40              | 52           |

he DA series combines complex analog and digital circuits allowing the integration of full systems on a single chip. The series is fully supported for customer designs using the Plessey advanced benchtop prototype modelling system allowing evaluation and verification of the design prior to silicon.

The chip architecture uses a central core of digital gates to implement the logic, surrounded by standard analog cells, for the analog and I/O functions characterised as an extensive range of macros. Each corner cell includes special components such as a voltage regulator, low offset and high current transistors, band gap reference and banks of closely matched resistors.

#### Plessey compiled ASIC

#### • SYSTEMS IN SILICON •

he Plessey Compiled ASIC is a technique developed through advances in CAE/CAD and the continuous development of Advanced Bipolar Process L. It allows the integration of complete systems, combining proven high performance analog, digital and memory functions. It is based on a single process technology.

Silicon compilation is used to design and optimise the digital sections of the chip and macros based on proven high performances off-the-shelf standard products provide the analog functions.

A comprehensive function/ macrofunction CAD supported library is available. This library is separated into three different areas, logic, memory and analog and interface.

Plessey Compiled ASICs offer

the benefits of greater cost effectiveness – via increased levels of integration, reduced inter-chip delays, and reduced noise and interference, with no compromise in performance, together with development timescales which allow faster entry into the market for the end product. To these benefits must be added the attributes of Process L, in respect of speed, analog performance, including accuracy and flexibility of I/O, and off-chip drive capability.

The basic analog and digital performance capability of the Compiled ASIC currently includes such features as:

Digital system speeds of up to 200MHz

Sub nanosecond gate delays

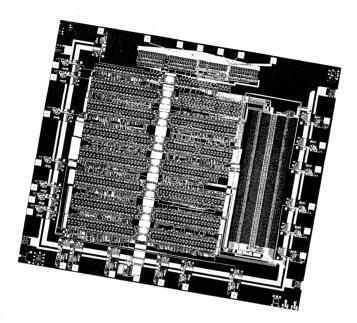

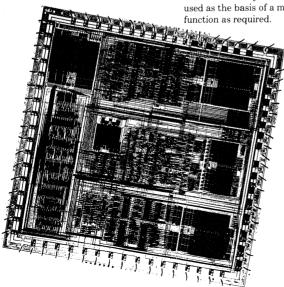

An example of the implementation of a Compiled ASIC solution to a system integration is shown in the photograph.

The circuitry combines 4 and 8-bit converters and high linearity VCOs with counters, adders, interface logic and high access speed ROM and drivers together with on-chip voltage regulation.

- A to D and D to A converters to 10 bit resolution

- Oscillators and Amplifiers up to 250MHz/250mW

- Comparators and Voltage references

- Control and bus drive interface protocol circuits

- High speed systolic array digital multipliers

- ROM to 8K bits with access times to 5ns

- RAM to 2K bits with access time to 5ns

- Output drive capability to a few hundred mA

Key to the performance of Compiled ASIC is Process L. This technology offers minimum feature sizes of 1.5 microns and double layer metal with pitches on both layers of 6 microns.

#### Bipolar analog/digital arrays

he DIGILIN array series combines high performance analog and digital functions on the same chip. The chips contain a core of Matrix cells, for implementing logic, surrounded by peripheral cells, for analog and I/O functions. Special components are located in the chip corners

# •DIGILIN •

| 'P' SER                              | IES DIGILIN                                   | ARRAYS                                  |                                                 |                                |

|--------------------------------------|-----------------------------------------------|-----------------------------------------|-------------------------------------------------|--------------------------------|

| ARRAY<br>Type                        | LOGIC<br>GATE COUNT                           | ANALOG<br>CELL COUNT                    | ANALOG<br>NPN COUNT                             | BOND<br>PADS                   |

| 1P                                   | 128                                           | 16                                      | 128                                             | 26                             |

| 2P                                   | 208                                           | 20                                      | 160                                             | 30                             |

| 3P                                   | 338                                           | 24                                      | 192                                             | 34                             |

| 4P                                   | 442                                           | 28                                      | 224                                             | 38                             |

| 6P                                   | 578                                           | 32                                      | 256                                             | 42                             |

| 9P                                   | 882                                           | 40                                      | 320                                             | · 50                           |

|                                      |                                               |                                         |                                                 |                                |

| 11P<br>G' SER                        | 1152<br>IES DIGILIN /                         | 44<br>ARRAYS                            | 352                                             | 54                             |

|                                      | · · · · · · · · · · · · · · · · · · ·         | • • • • • • • • • • • • • • • • • • • • | 352  ANALOG NPN COUNT                           | 54  BOND PADS                  |

| G' SER<br>array                      | IES DIGILIN /                                 | ARRAYS<br>analog                        | ANALOG                                          | BOND                           |

| G' SER<br>array<br>type              | LOGIC<br>GATE COUNT                           | ARRAYS  ANALOG  CELL COUNT              | ANALOG<br>NPN COUNT                             | BOND<br>PADS                   |

| G' SER<br>ARRAY<br>TYPE              | LOGIC GATE COUNT                              | ARRAYS  ANALOG CELL COUNT               | ANALOG<br>NPN COUNT                             | BOND<br>PADS                   |

| G' SER  ARRAY TYPE  03G 1G 2G        | LOGIC<br>GATE COUNT                           | ARRAYS  ANALOG CELL COUNT  10 16        | ANALOG<br>NPN COUNT<br>120<br>192               | BOND<br>PADS<br>18<br>24       |

| G' SER  ARRAY TYPE  03G 1G 2G 3G     | LOGIC<br>GATE COUNT<br>30<br>98<br>162        | ARRAYS  ANALOG CELL COUNT  10 16 20     | ANALOG NPN COUNT  120 192 240                   | BOND<br>PADS<br>18<br>24<br>28 |

| G' SER<br>ARRAY<br>TYPE<br>03G<br>1G | LOGIC<br>GATE COUNT<br>30<br>98<br>162<br>242 | ARRAYS  ANALOG CELL COUNT  10 16 20 24  | ANALOG<br>NPN COUNT<br>120<br>192<br>240<br>288 | BOND PADS  18 24 28 32         |

such as: a band gap reference, high current transistors, capacitors and banks of closely matched resistors. Typical analog functions include Schmitt triggers, regulators, comparators, op-amps, monostables, oscillators, ceramic resonators, white noise sources, peak reading circuits, data converter functions.

#### Features:

- Digital and analog circuitry on a single chip.

- Operation from 1 to 15 volt supply. (12 volts on 'G' Series)

- High current drive capability (250mA 'G' Series, 120mA 'P' Series).

- Complete system integration capability.

- Reduced system space and power

- Rapid development time.

The 'P' and 'G' series of Digilin arrays both have 7 arrays of varying complexity. The G series is intended for analog dominated systems with 50% of the chip devoted to analog and I/O functions. The P series has a higher digital content with 75% of the chip allocated to the digital matrix.

Peripheral transistors have a typical gain of 150 which is flat over 8 current decades. Matching is typically 1%.

High performance analog designs are accomplished using the tight matching of the peripheral active and passive components. Precharacterised analog macros and full CAD simulation support gives a complete design environment for total system integration.

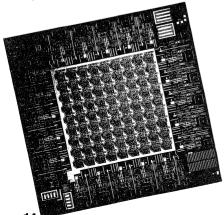

#### Plessey MEGACELL

he MEGACELL approach provides a cell-based design methodology for highefficiency CMOS designs. All cells are committed (unlike gate arrays) so in general more complex designs are possible. Plessey MEGACELL is very suitable for integrating up to full-custom complexity, without the long development timescales and high costs associated with full-custom. Fast circuit development is possible by using the Plessey Design System (PDS2) linked to the MEGACELL

Plessey Megacell is available in both 2 micron and 1.4 micron technologies. These are designated MVA 5000 series and MVA 60000 series respectively and allow circuits of up to 35,000 gate equivalents to be realised on MVA 5000 and 80,000 on MVA 60000.

design libraries.

MEGACELL libraries provide functional, dynamic and physical models of a wide range of functions, both analog and digital. These cells range from simple logic functions (microcclls) to complex parameterisable functions (Paracells) and complex standard functions (Supracells).

#### • SYSTEMS IN SILICON •

#### Cell Library Types

For both Gate Arrays and MEGACELL designs, Plessey Semiconductors classifies library cells into groups. Every cell is supported by a logical design model, which includes all relevant data for the software design tools (eg, testability, functional and timing data), plus a physical design model for the software layout (eg, cell boundaries, pin nodes, routing areas). The cell groups are as follows:-

#### Microcells

Microcells are the simplest cells in the library. They are similar in function and complexity to those available in 74 series TTL and 4000 series CMOS standard products and include basic logic gates such as NAND, NOR, D-type flip-flops, etc.

Macrocells

Macrocells are the next level in the hierarchy of cells and have been designed using microcells. Plessey Macrocells comprise a collection of the larger functions most used in the 74 series TTL and 4000 series CMOS MSI products. A full cell-list description of these macrocells is provided to

the user and may be changed and used as the basis of a modified function as required.

Shorter design time – large functions need not be designed from scratch:

Designers can use more familiar MSI design blocks;

Some circuits can be translated directly from breadboards built from standard TTL/CMOS parts.

#### Supracells

Supracells are equivalent to large complex functions, which again have their own specific logical and physical design models for the software design tools.

These cells include complex multipliers, DSP functions, bit slice processors etc.

#### Paracells

Paracells are medium to large scale cells which are algorithmically generated by the PDS2 software from simple descriptions entered by the designer.

Functions available as Paracells include RAM, ROM, PLA, Register Files, Multipliers and ALUs.

In the case of RAM, for example, the user simply specifies the address length, the word length and the number of words, as a one line command to PDS2. The software then compiles both the simulation model and the physical models of the required memory, working only from this simple instruction.

#### Analog Functions

Appreciating that in real applications both digital and analog functions must interface to each other, the MEGACELL library supports a range of analog functions, including:-

- Op Amps

- Comparators

- R-C Oscillators

- ADC and DAC functions.

- Capacitive and Resistive elements.

## The Quality Concept

Quality cannot be inspected into a product; it is only by careful design and evaluation of materials, parts and processes (followed by strict control and ongoing assessment) that quality products will be produced.

All designs conform to standard layout rules, all processes are thoroughly evaluated and all new piece part designs and suppliers are investigated before authorisation for production use

The same basic procedures are used on all products up to and including device packing. It is only then that extra operations are performed for certain customers in terms of lot qualification or release procedure.

By working to common procedures all users benefit; the high reliability user gains the advantage of scale hence improving the confidence factor in the quality achieved, whilst the volume user gains the benefits of basic high reliability design concepts.

Plessey Semiconductors have the following factory approvals:

**BS9300** and **BS9400** (BSI Approval No. 1053/M).

CECC50000 and CECC90000 (Reg. No. M/0020/CECC/UK-1053/M).

DEF-STAN 05-21 (DCL Reg. No. 1SB PO1).

Plessey Semiconductors conforms to MIL-M-38510F and is qualified to supply to MIL-STD-883C.

#### Screening

Different screening procedures are carried out by Plessey Semiconductors Limited, a brief description of the differences involved are explained in the next few pages.

| Stage/Operation                           | PLESSEY HI-REL CLASS B<br>(References are to MIL-STD-883C) | MIL-STD-883C CLASS B<br>Method 5004                    |

|-------------------------------------------|------------------------------------------------------------|--------------------------------------------------------|

| Internal Visual                           | Method 2010<br>Test Condition B 100%                       | Method 2010<br>Test Condition B 100%                   |

| Stabilisation Bake                        | Method 1008<br>24 Hrs at Condition C 100%                  | Method 1008<br>24 Hrs at Condition C 100%              |

| Temperature Cycling                       | Method 1010<br>Test Condition C 100%                       | Method 1010<br>Test Condition C 100%                   |

| Constant Acceleration                     | Method 2001<br>Test condition E Y1 only. 100%              | Method 2001<br>Test Condition E Y1 only. 100%          |

| Visual Inspection                         | -                                                          | 100 %                                                  |

| Initial Electrical                        | Those parameters requiring Delta calculations. 100%        | Those parameters requiring Delta calculations. 100%    |

| Burn-In                                   | Method 1015<br>160 Hrs at 125°C min. 100%                  | Method 1015<br>160 Hrs at 125°C min. 100%              |

| Post Burn-In<br>Electrical Test           | Full Electrical Test to guarantee Data Sheet. 100%         | Those parameters requiring<br>Delta Calculations. 100% |

| PDA Calculation                           | 5 % max. All lots.                                         | 5 % max. All lots.                                     |

| Final Electrical Test                     | Done as Post Burn-in Test 100%                             | Full Group A tests as Method 5005 100%                 |

| Seal (a) Fine<br>Seal (b) Gross           | Method 1014 100%                                           | Method 1014 100%                                       |

| Qualification/Quality<br>Conformance Test |                                                            | Method 5005 Class B<br>Samples as necessary            |

| External Visual                           | Plessey Spec. sample                                       | Method 2009 100%                                       |

| Stage/<br>Operation  | Standard<br>Product    | Plessey<br>Hi-Rel B | MIL-STD-883C<br>Class B                  | MIL-STD-883C<br>Class S            | BS9400<br>Level S2                       |

|----------------------|------------------------|---------------------|------------------------------------------|------------------------------------|------------------------------------------|

| Coding<br>(example)  | SPxxxxA                | SPxxxxAB            | SPxxxxAC                                 | SPxxxxAS                           | SPxxxxABSS2                              |

| Wafer-fab            |                        |                     |                                          | Wafer-lot<br>accept<br>Method 5007 |                                          |

| Probe test           | 100 %                  | 100 %               | 100 %                                    | 100 %                              | 100 %                                    |

| Visual inspect chips | Usually 2010<br>Cond B | 2010<br>Cond B      | 2010<br>Cond B                           | 2010<br>Cond A                     | BS9400<br>1.2.10 Cond B                  |

| Assemble             |                        |                     |                                          | Includes<br>100 % bond<br>pull     |                                          |

| Screen               | None                   | As list attached    | Method 5004<br>Class B                   | Method 5004<br>Class S             | BS9400<br>1.2.9 Level B                  |

| Test                 | 100 %                  | 100 %               | 100 %                                    | 100 %                              | 100 %                                    |

| Conformance testing  | None                   | None                | Method 5005<br>Class B                   | Method 5005<br>Class S             | BS9400                                   |

|                      |                        |                     | Group A<br>Group B<br>Group C<br>Group D | Group A<br>Group B<br>Group D      | Group A<br>Group B<br>Group C<br>Group D |

| Ship                 |                        |                     |                                          |                                    |                                          |

#### **NOTES**

- 1. Visual inspection BS9400 1.2.10 Cond B is equivalent to MIL-STD-883 Method 2010 Cond B.

- 2. Screening BS9400 1.2.9 Level B is equivalent to MIL-STD-883 Method 5004 Class B EXCEPT it does not include 100% hot and cold test.

- 3. Conformance testing BS9400 is similar to MIL-STD-883 Class B EXCEPT:

- Group A does not necessarily include hot and cold testing.

- Group B does include 160 hour operating life test.

- Group C does include 2000 hour operating life test and hot and cold testing.

- Group D only usually includes 8000 hour life test and dimension checks.

# Technical Data

#### SL560C 300MHz LOW NOISE AMPLIFIER

This monolithic integrated circuit contains three very high performance transistors and associated biasing components in an eight-lead TO-5 package forming a 300MHz low noise amplifier. The configuration employed permits maximum flexibility with minimum use of external components. The SL560C is a general purpose low noise, high frequency gain block

The device is also available as the SL560AC which has guaranteed operation over the full Military Temperature Range and is screened to MIL-STD-883C Class B. Data is available separately.

#### **FEATURES**

- Gain up to 40dB

- Noise Figure less than 2dB (Rs 200 ohm)

- Bandwidth 300MHz

- Supply Voltage 2-15V (Depending on Configuration)

- Low Power Consumption

#### **APPLICATIONS**

- Radar IF Preamplifiers

- Infra-Red Systems Head Amplifiers

- Amplifiers in Noise Measurement Systems

- Low Power Wideband Amplifiers

- Instrumentation Preamplifiers

- 50 ohm Line Drivers

- Wideband Power Amplifiers

- Wide Dynamic Range IF Amplifiers

- Aerial Preamplifiers for VHF TV and FM Radio

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage (Pin 4)      | +15V                    |

|-----------------------------|-------------------------|

| Storage temperature         | -55°C to 150°C (CM)     |

| Otolog III                  | -55°C to 125°C (DP)     |

| Junction temperature        | 150°C (CM) 125°C (DP)   |

| Thermal resistance          |                         |

| Junction-case               | 60°C/W (CM)             |

| Junction ambient 220        | 0°C/W (CM) 230°C/W (DP) |

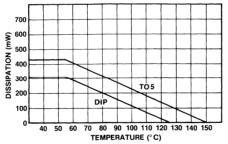

| Maximum power dissipation   | See Fig.15              |

| Operating temperature range | = -55°C to +125°C (CM)  |

| Operating temperature       | at 100mW                |

|                             | -55°C to +100°C (DP)    |

|                             | at 100mW                |

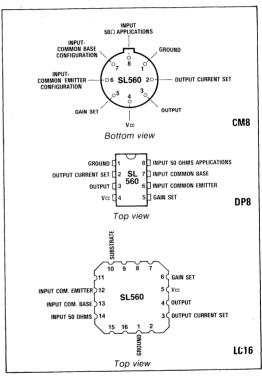

Fig.1 Pin connections

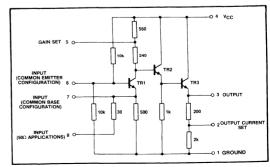

Fig.2 SL560C circuit diagram

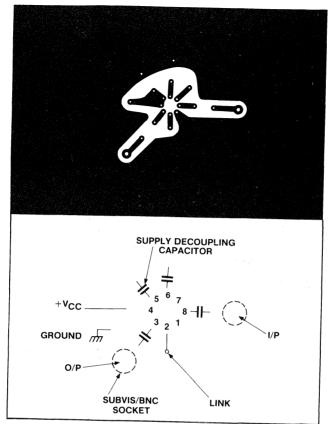

Fig.3 PC layout for  $50\Omega$  line driver (see Fig.6)

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

Frequency = 30MHz; Vcc = 6V;  $Rs = RL = 50\Omega$ ;  $T_{amb} = 25$  °C; Test Circuit: Fig.6

| Characteristic                |      | Value |      | Units | Conditions       |

|-------------------------------|------|-------|------|-------|------------------|

|                               | Min. | Тур.  | Max. | Units |                  |

| Small signal voltage gain     | 11   | 14    | 17   | dB    |                  |

| Gain flatness                 |      | ±1.5  |      | dB    | 10MHz - 220MHz   |

| Upper cut-off frequency       |      | 250   |      | MHz   |                  |

| Output swing                  | +5   | +7    |      | dBm   | Vcc6V See Fig.5  |

|                               |      | +11   |      | dBm   | $V_{CC} = 9V$    |

| Noise figure (common emitter) |      | 1.8   |      | dB    | $Rs = 200\Omega$ |

|                               |      | 3.5   |      | dB    | $Rs = 50\Omega$  |

| Supply current                |      | 20    | 30   | mA    |                  |

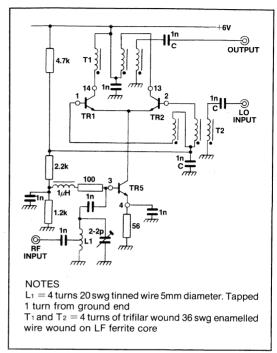

#### CIRCUIT DESCRIPTION

Three high performance transistors of identical geometry are employed. Advanced design and processing techniques enable these devices to combine a low base resistance (Rbb') of 17Ω (for low noise operation) with a small physical size giving a transition frequency, f<sub>1</sub>, in excess of 1GHz.

The input transistor (TR1) is normally operated in common base, giving a well defined low input impedance. The full voltage gain is produced by this transistor and the output voltage produced at its collector is buffered by the two emitter followers (TR2 and TR3). To obtain maximum bandwidth the capacitance at the collector of TR1 must be minimised. Hence, to avoid bonding pad and can capacitances, this point is not brought out of the package. The collector load resistance of TR1 is split, the tapping being accessible via pin 5. If required, an external roll-off capacitor can be fixed to this point.

The large number of circuit nodes accessible from the outside of the package affords great flexibility, enabling the

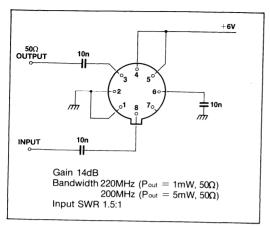

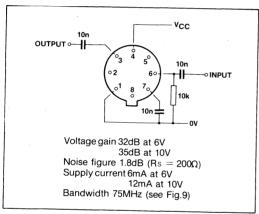

operating currents and circuit configuration to be optimised for any application. In particular, the input transistor (TR1) can be operated in common emitter mode by decoupling pin 7 and using 6 as the input. In this configuration, a 2dB noise figure (Rs =  $200\Omega$ ) can be achieved. This configuration can give a gain of 35dB with a bandwidth of 75MHz (see Figs. 8 and 9) or, using feedback 14dB with a bandwidth of 300MHz (see Figs. 10 and 11).

Because the transistors used in the SL560C exhibit a high value of  $f\tau$ , care must be taken to avoid high frequency instability. Capacitors of small physical size should be used, the leads of which must be as short as possible to avoid oscillation brought about by stray inductance. The use of a ground plane is recommended.

Further applications information is available in the 'Broadband Amplifier Applications' booklet.

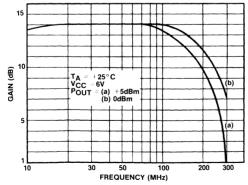

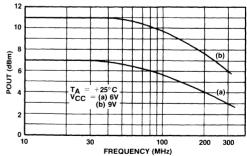

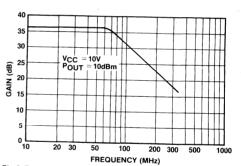

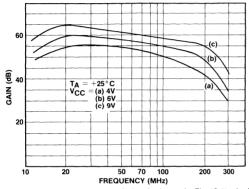

Fig.4 Frequency response, small signal gain is of a typical device

Fig.5 Frequency response, output capability (loci of maximum output power with frequency, for 1dB gain compression (typical)

#### SL560C

#### TYPICAL APPLICATIONS

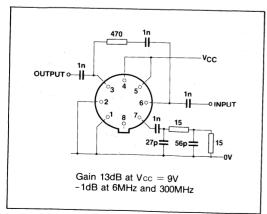

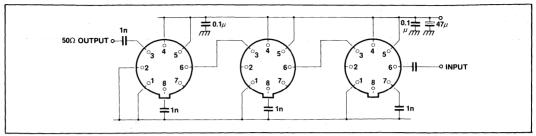

Fig.6 50  $\!\Omega$  line driver. The response of this configuration is shown in Fig.4.

Fig.8 Low noise preamplifier

Fig.10 Wide bandwidth amplifier

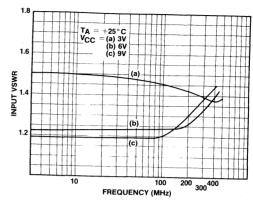

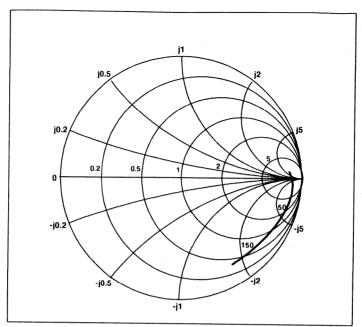

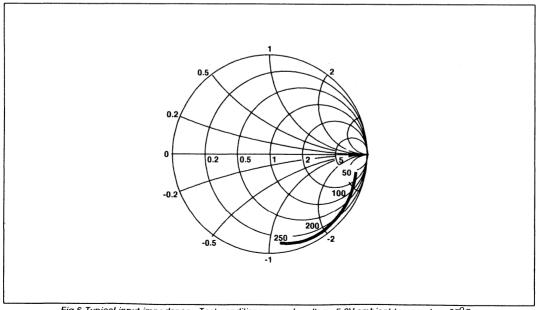

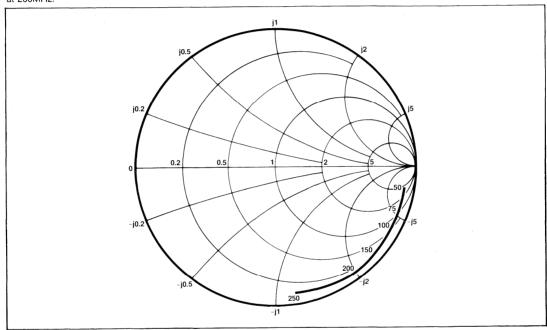

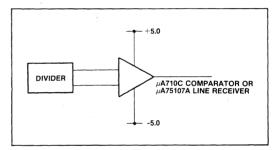

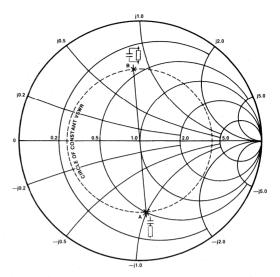

Fig.7 Input standing wave ratio plot of circuit shown in Fig.6 (typical)

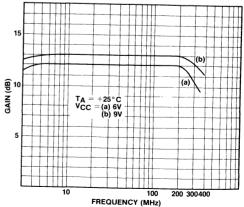

Fig.9 Frequency response of circuit shown in Fig.8 (typical)

Fig.11 Frequency response of circuit shown in Fig.10 (typical)

Fig.12 Three-stage directly-coupled high gain low noise amplifier

Fig.13 Frequency response of circuit shown in Fig.12 (typical)

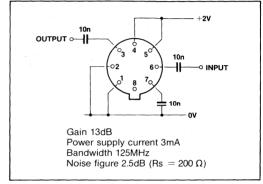

Fig.14 Low power consumption amplifier

Fig.15 Ambient operating temperature v. degrees centigrade (typical)

#### **SL562**

#### LOW NOISE PROGRAMMABLE OPERATIONAL AMPLIFIER

The SL562 is an advanced bipolar integrated circuit containing a single programmable operational amplifier. The amplifier can be programmed by current into a bias pin which determines the main characteristics of the amplifier's, supply current, frequency response and slew rate. With a suitable choice of bias current the SL562 can be used where low power and low noise characteristics are a necessity.

#### **FEATURES**

- Low Noise Guaranteed (25nV/√Hz at 1kHz)

- Low Supply Current (40uA)

- Bias Conditions Adjustable to Optimise Performance

- Built In Short Circuit Protection

- Available In Small Outline

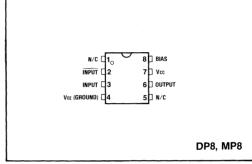

Fig.1 Pin connections - top view

#### **APPLICATIONS**

- Active Filters

- Oscillators

- Low Voltage Amplifiers

- Frequency Synthesisers

- Hand Held Radio Applications

#### QUICK REFERENCE DATA

- Supply Voltages ±1.5V to ±10V

- Supply Current ±40µA to ±2mA

- Operating Frequency Range 1MHz

- Gain 95dB

- Operating Temperature Range -40°C to +85°C

Fig.2 Circuit diagram.

#### **ELECTRICAL CHARACTERISTICS**

#### Test conditions (unless otherwise stated):

$T_{amb} = 25^{\circ} C$

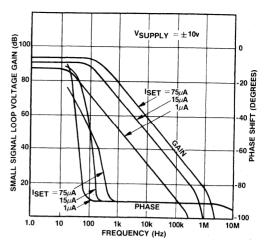

Operating mode A : Supply volts  $\pm 10V$  Bias set current  $75\mu$ A Operating mode B : Supply volts  $\pm 3.5V$  Bias set current  $15\mu$ A Operating mode C : Supply volts  $\pm 1.5V$  Bias set current  $1\mu$ A

Operating mode Characteristic Conditions C Units Min. Тур. Max. Min. Max. Min. Max. Typ. Typ. Input offset voltage  $Rs = 10k\Omega$ 1 5 1 5 1 5 m۷ Input offset current 20 190 150 49 nΑ 250 800 350 95 Input bias current nΑ Input resistance 0.1 0.6 0.2 0.5 0.3 2 МΩ 1000 1600 2200 50 200 1000 40 Supply current 20 60 μΑ 74 Large signal 74 95 90 74 90 dB  $R_L = 4k\Omega(A)$ voltage gain  $R_L = 100k\Omega(B)$  $R_L = 100k\Omega(C)$ Input voltage range 10 10.5 10 10.5 0.2 0.4  $Rs = 10k\Omega$ 70 110 70 85 Common mode 70 82 dB rejection ratio Output voltage swing 8 1.5 0.7 0.8  $\pm V$  $R_L = 4k\Omega(A)$  $R_L = 10k\Omega(B)$  $R_L = 4k\Omega(C)$ 85  $Rs = 10k\Omega$ Supply voltage 74 85 dB rejection ratio Short circuit current 12 40  $T_{amb} = 0^{\circ} C$ 2.2 1 mΑ to +70°C Gain bandwidth Gain = 20dB 50 kHz product 3.5 1 MHz Slew rate 1.5 0.5 0.02 V/μs Gain = 20dB Input noise voltage 10 25 25 40 50 85 nV√Hz fo = 1kHzpA√Hz Input noise current 1.6 1.6 1.0 f = 1kHz

#### **OPERATING NOTES**

#### Bias set current

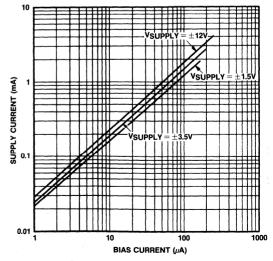

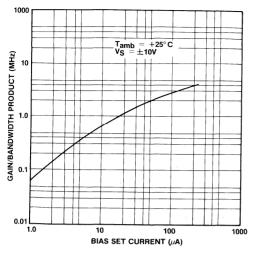

The amplifier is programmed by the ISET current into the BIAS pin to determine the frequency response, slew rate and the value of supply current. The relationship is summarised as follows:

Gain bandwidth product  $1 \text{SET } \times 50 \text{kHz}$  Power supply current (each supply)  $1 \text{SET } \times 25 \mu \text{A}$  Slew rate  $1 \text{SET } \times 0.02 \text{V}/\mu \text{S}$   $1 \text{SET } \times 0.02 \text{V}/\mu \text{S}$   $1 \text{SET } \times 0.02 \text{V}/\mu \text{S}$   $1 \text{SET } \times 0.02 \text{V}/\mu \text{S}$

The open loop voltage gain is largely unaffected by change in bias set current but tends to peak slightly at 10µA. Since the voltage on the BIAS pin is approximately 0.65V more positive than the negative supply, a resistor may be

more positive than the negative supply, a resistor may be connected between the bias pin and either 0V or the positive supply to set the current. Thus, if the resistor is connected to 0V, the ISET current is determined by:

$$I_{SET} = \frac{V_{S} - 0.65}{R}$$

where R is value of the 'set' resistor.

The output goes high if the non-inverting input is taken lower than 1V above the negative power supply.

Fig.3 Supply current v. bias set current.

Fig.4 Gain bandwidth product v. ISET

Fig. 5 Typical frequency response

#### APPLICATION EXAMPLE

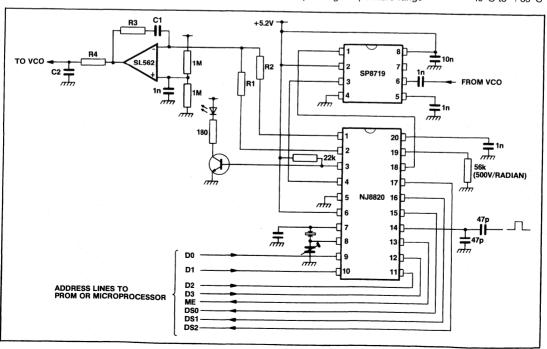

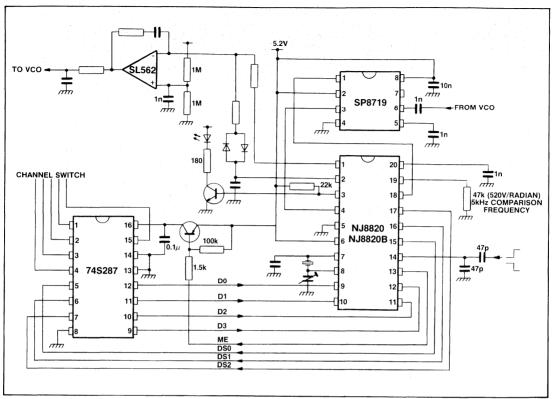

The SL562 is especially suitable for use in loop filters for frequency synthesisers, the low noise and low power characteristics of the SL562 making it ideally suited for use with the Plessey low power frequency synthesiser circuits (NJ8820, SP87XX). All three integrated circuits are available in surface mounting packages, thus making a compact hybrid.

#### **ABSOLUTE MAXIMUM RATINGS**

Supply voltages  $\pm 15V$ Common mode input voltage Not greater than supplies Differential input voltage  $\pm 25V$ Bias set current 10mA Storage -55° C to +125° C Power dissipation 800mW at 25° C Derate at 7mW/° C above 25° C Operating temperature range -40° C to +85° C

Fig.6 Application example.

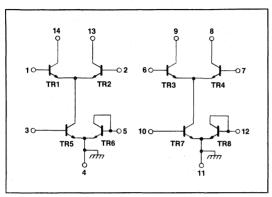

#### SL2363C & SL2364C

#### **VERY HIGH PERFORMANCE TRANSISTOR ARRAYS**

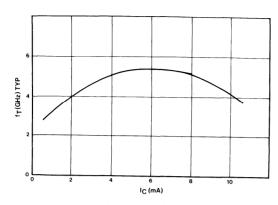

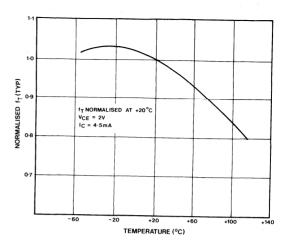

The SL2363C and SL2364C are arrays of transistors internally connected to form a dual long-tailed pair with tail transistors. They are monolithic integrated circuits manufactured on a very high speed bipolar process which has a minimum useable fr of 2.5GHz, (typically 5GHz).

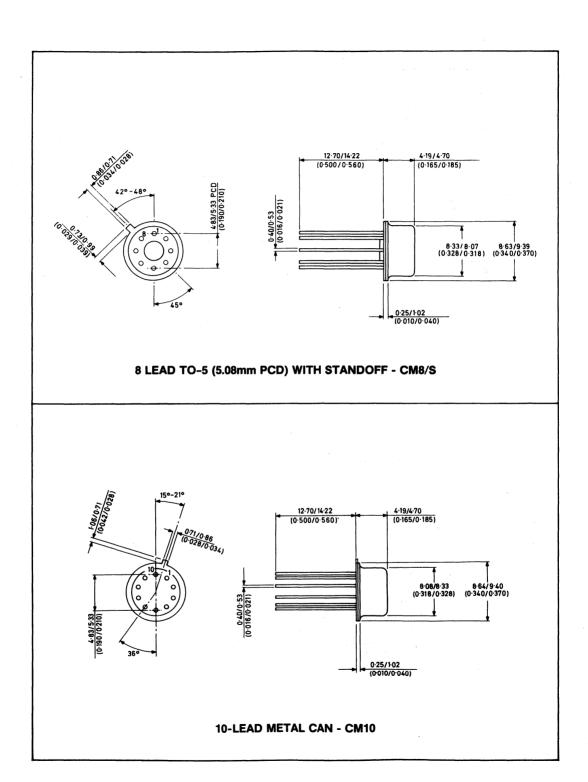

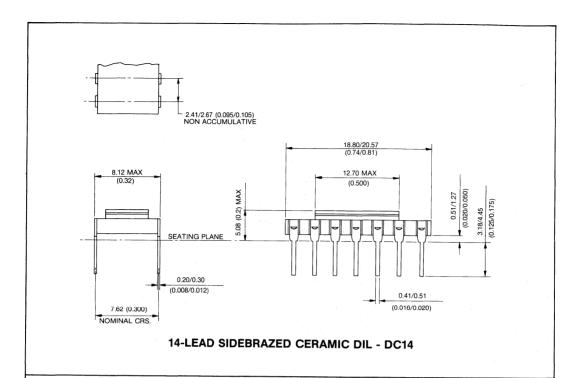

The SL2363 is in a 10 lead TO5 encapsulation.

The SL2364 is in a 14 lead DIL plastic encapsulation and a high performance Dilmon encapsulation.

#### **FEATURES**

- Complete Dual Long-Tailed Pair in One Package.

- Very High f<sub>T</sub> Typically 5 GHz

- Very Good Matching Including Thermal Matching

#### **APPLICATIONS**

- Wide Band Amplification Stages

- 140 and 560 MBit PCM Systems

- Fibre Optic Systems

- High Performance Instrumentation

- Radio and Satellite Communications

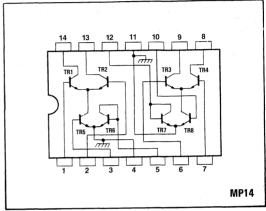

# SL 2363C CM10 SL 2364C DC14 DP14 MP14

Fig. 1 Pin connections (top view)

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

$T_{amb} = 22^{\circ}C \pm 2^{\circ}C$

| Characteristics                                                                    |                                   | Value                                                      |                 |                                             |                                                                                                                                                        |

|------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------|-----------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                    | eristics Min. Typ. Max.           |                                                            | Max.            | Units                                       | Conditions                                                                                                                                             |

| BVCBO LVCEO BVEBO BVCIO hFE fr $\Delta$ VBE (See note 1) $\Delta$ VBE/TAMB CCB CCI | 10<br>6<br>2.5<br>16<br>50<br>2.5 | 20<br>9<br>5.0<br>40<br>80<br>5<br>2<br>-1.7<br>0.5<br>1.0 | 5<br>0.8<br>1.5 | V<br>V<br>V<br>V<br>GHz<br>mV°C<br>pF<br>pF | IC = 10µA<br>IC = 5mA<br>IE = 10µA<br>IC = 10µA<br>IC = 8mA, VCE = 2V<br>IC (Tail) = 8mA, VCE = 2V<br>IC (Tail) = 8 mA, VCE = 2V<br>VCB = 0<br>VCI = 0 |

NOTE 1.  $\Delta V_{BEQ3} - V_{BEQ4}$  and  $V_{BEQ5} - V_{BEQ6}$

#### SL2363C & SL2364C

#### TYPICAL CHARACTERISTICS

Fig. 2 Collector current

Fig. 3 Chip temperature

#### **ABSOLUTE MAXIMUM RATINGS**

Maximum individual transistor dissipation 200mW

Storage temperature -55°C to +150°C Maximum junction temperature +150°C Package thermal resistance (°C/W);

Chip to case 65 (CM10)

Chip to ambient 225 (CM10) 175 (DP14)

$V_{CBO} = 10V$ ,  $V_{EBO} = 2.5V$ ,  $V_{CEO} = 6V$ ,  $V_{CIO} = 15V$ , IC (any one transistor) = 20mA

The substrate should be connected to the most negative point of the circuit to maintain electrical isolation between the transistors.

# SL2365 VERY HIGH PERFORMANCE TRANSISTOR ARRAY

The SL2365 is an array of transistors internally connected to form a dual long-tail pair with current mirrors whose bases and collectors are connected internally. The ICs are manufactured on a very high speed bipolar process, which has a minimum usable  $f\tau$  of 2.5GHz (typically 5GHz). The current mirror enables a well defined gain at low current levels to be achieved.

#### **FEATURES**

- Complete Dual Long Tailed Pair in One Package

- Very High ft Typically 5GHz

- Well Defined Gain at Low Current Levels

- Available in Small Outline Package

#### CAUTION

Pins 4 and 11 should be equal and at the most negative voltage on the array.

Fig.1 Pin connections - top view

#### **ELECTRICAL CHARACTERISTICS**

| Characteristic  |      | Value |      |       | Conditions                 |  |

|-----------------|------|-------|------|-------|----------------------------|--|

|                 | Min. | Тур.  | Max. | Units | Conditions                 |  |

| BVcbo           | 10   | 20    |      | V     | Ic = 10μA                  |  |

| LVceo           | 6    | 9     |      | V     | Ic = 5mA                   |  |

| BVebo           | 2.5  | 5     |      | V     | $I_E = 10\mu A$            |  |

| BV cio          | 16   | 40    | 1    | V     | Ic = 10μA                  |  |

| H <sub>fe</sub> | 50   | 80    |      |       | Ic = 8mA, Vce = 2V         |  |

| fτ              | 2.5  | 5     |      | GHz   | Ic (tail) = 8mA, V ce = 2V |  |

| ΔVbe            |      | 2     | 5    | mV    | Ic (tail) = 8mA, Vce = 2V  |  |

| ΔV be/T amb     |      | -7    |      | mV/°C | Ic (tail) = 8mA, Vce = 2V  |  |

| Ссв             |      | 0.5   | 0.8  | pF    | VcB = 0V                   |  |

| Cal             | l    | 1.0   | 1.5  | pF    | Vci = 0V                   |  |

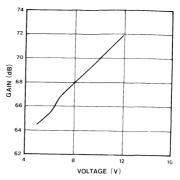

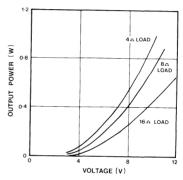

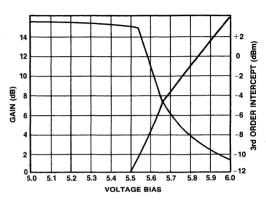

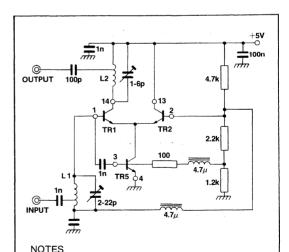

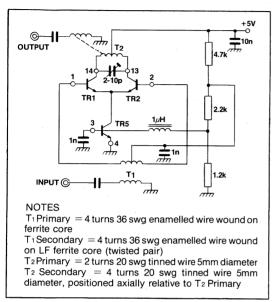

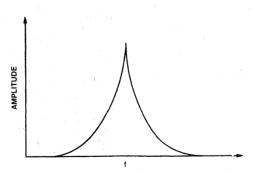

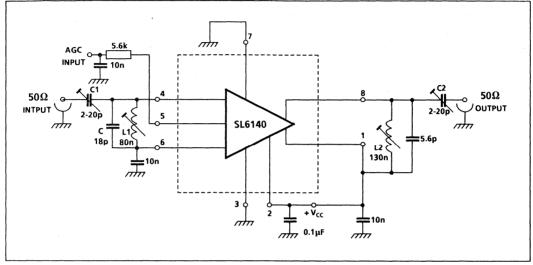

#### **SL6140**

#### **400MHz WIDEBAND AGC AMPLIFIER**

(Supersedes edition in September 1988 Linear IC Handbook)

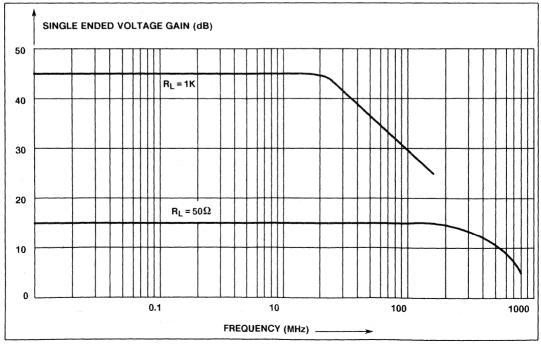

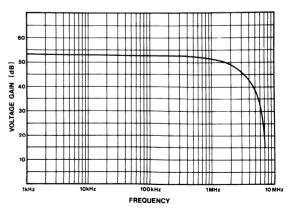

The SL6140 is an integrated broadband AGC amplfier, designed on an advanced 3-micron all implanted bipolar process. The amplfier provides over 15dB of linear gain into  $50\Omega$  with a 400MHz bandwidth.

Accurate gain control is also provided with over 70dB of dynamic range.

The SL6140 provides over 45dB of voltage gain with an  $R_{\rm L}$  of 1k $\Omega.$

#### **FEATURES**

- **400MHz** Bandwidth ( $R_L = 50\Omega$ )

- High Voltage Gain 45dB ( $R_1 = 1k\Omega$ )

- 70dB Gain Control Range

- High Output Level at Low Gain

- Accurate Gain Control

- MC1590 Replacement

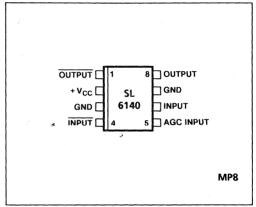

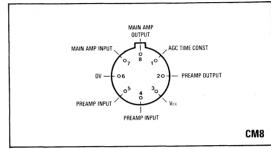

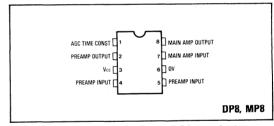

Fig.1 Pin connections (top view)

#### **APPLICATIONS**

- RF/IF Amplifier

- High Gain Mixers

- Video Amplifiers

#### **ORDERING INFORMATION**

SL6140 MP (Industrial - Miniature Plastic DIL Package)

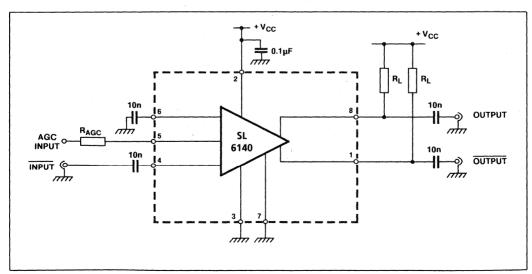

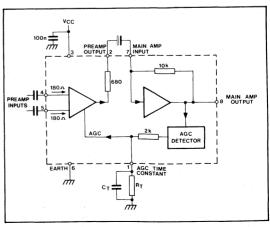

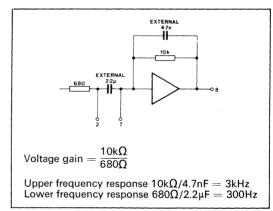

Fig.2 Typical wideband application ( $R_{AGC} = 5.6k$ )

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

Tamb = 25°C, VCC = + 12V

| Characteristic                                                             | Pin          | Value    |     |     |       |                                 |

|----------------------------------------------------------------------------|--------------|----------|-----|-----|-------|---------------------------------|

|                                                                            | Pin          | Min      | Тур | Max | Units | Conditions                      |

| Supply current                                                             | 1,2,8        | -        | 19  | 23  | mA    |                                 |

| Output stage current                                                       | 1,8<br>(sum) | 5        | 7   | 9   | mA    |                                 |

| Output current matching<br>(magnitude of difference of output<br>currents) | 1,8          | )        | 0.5 | -   | mA    |                                 |

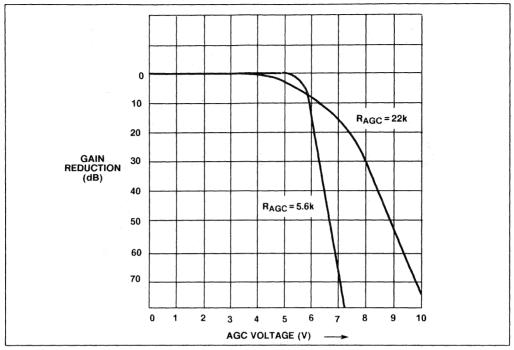

| AGC range                                                                  | 5            | 60       | 75  | Ī   | dB    | See Fig. 4                      |

| Voltage gain (single ended)                                                | 1,8          | 40       | 45  | -   | dB    | R <sub>L</sub> = 1kΩ See Fig.5  |

|                                                                            |              |          | 55  |     | dB    | Tuned input and output          |

|                                                                            | 1,8          | <u>-</u> | 15  | -   | dB    | $R_L = 50\Omega$                |

| Bandwidth (-3dB)                                                           | 1,8          | -        | 25  | -   | MHz   | R <sub>L</sub> = 1kΩ See Fig. 5 |

|                                                                            |              |          | 400 |     | MHz   | $R_L = 50\Omega$                |

| Maximum output level (single ended)                                        |              |          |     |     |       |                                 |

| 0dB AGC                                                                    | 1,8          | 2.5      | 3.5 | -   | V р-р | $R_L = 1k\Omega$                |

| -30dB AGC                                                                  | 1,8          | 2.5      | 3.5 | -   | V р-р | $R_L = 1k\Omega$                |

#### DESCRIPTION

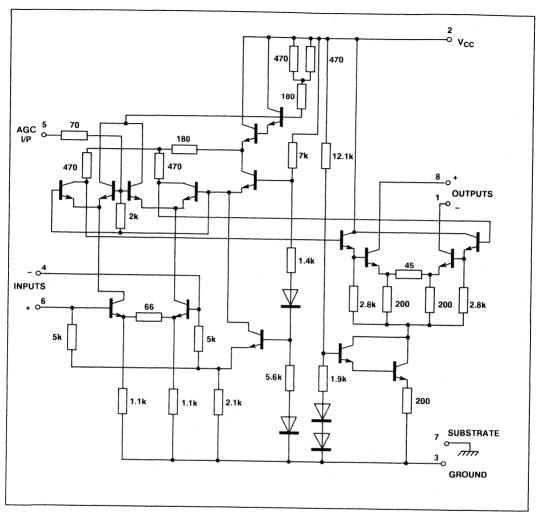

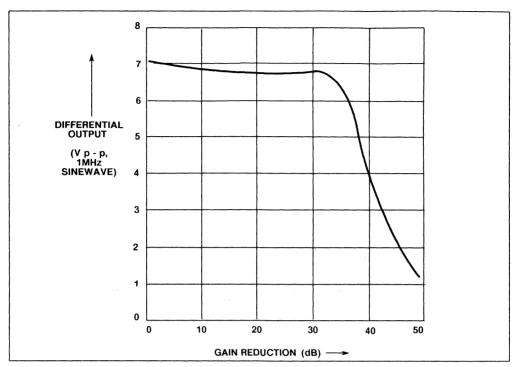

The SL6140 (Fig.3) is a high gain amplifier with an AGC control capable of reducing the gain of the amplifier by over 70dB. The gain is adjustable by applying a voltage to the AGC input via an external resistor (RAGC, the value of which adjusts the curve of gain reduction versus control voltage (see Fig. 4) As the output stage of the amplifier is an open collector the maximum voltage gain is determined by  $R_L$ . With load resistance of  $1k\Omega$  the single ended voltage gain is 45dB and with a load resistance of  $50\Omega$  the voltage gain is 15dB (20log<sub>10</sub> VOUT/VIN). Another parameter that depends on the load resistance is the bandwidth: 25MHz for  $R_1 = 1k\Omega$ , as compared with 400MHz for  $R_L = 50\Omega$ .  $R_L$  is chosen to give either the required bandwidth or voltage gain for the circuit.

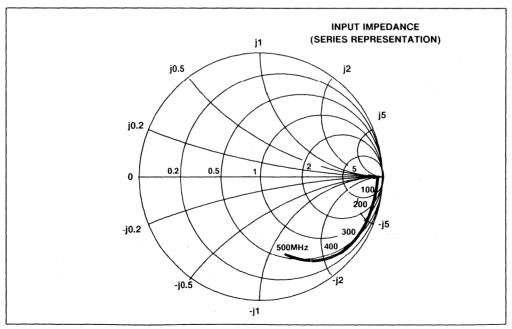

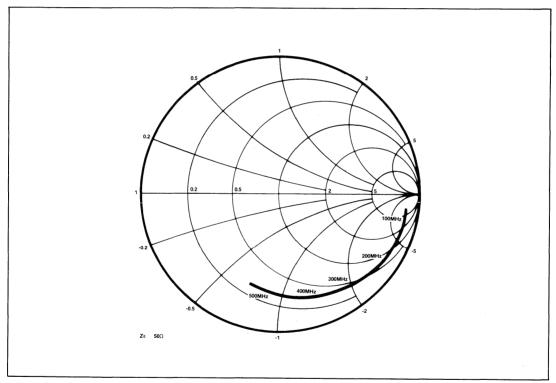

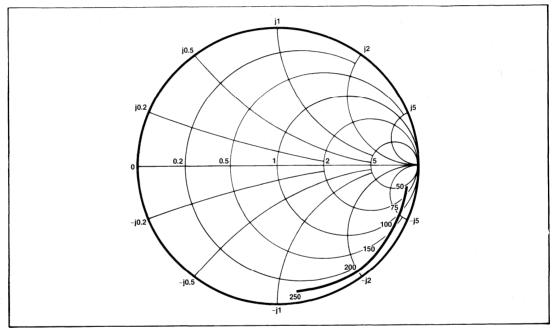

Fig. 7 shows the input impedance of the device. Accurate impedance matching to both inputs and outputs of this device (by resonant circuit or other means) can raise the gain to 55dB but for most circumstances a  $50\Omega$ source impedance is adequate.

#### ABSOLUTE MAXIMUM RATINGS

Supply voltage, V<sub>CC</sub> Input voltage (differential) AGC Supply V<sub>CC</sub> -55°C to + 125°C Storage temperature Operating temperature 0°C to 70°C

+ 15V

+ 5V

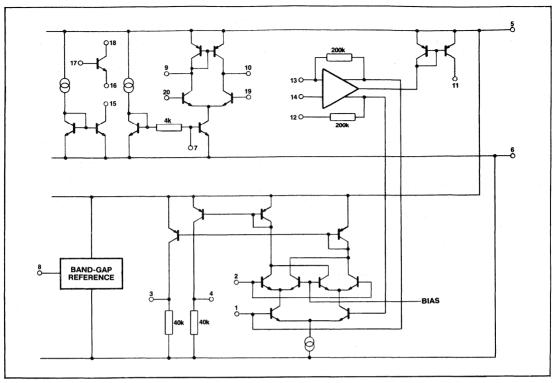

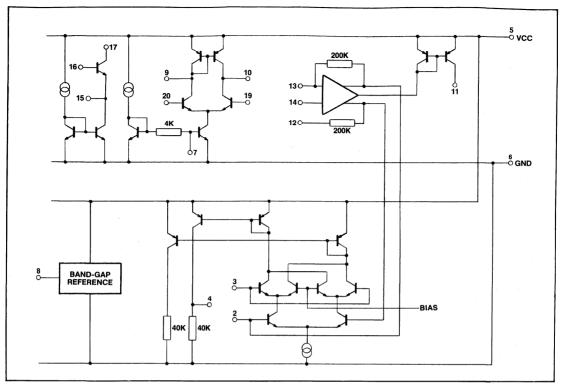

Fig. 3 - Full circuit diagram of \$L6140

Fig. 4 - Gain reduction v. AGC Voltage

Fig. 5 - Voltage gain v. frequency

Fig. 6 - Maximum differential output v. gain reduction

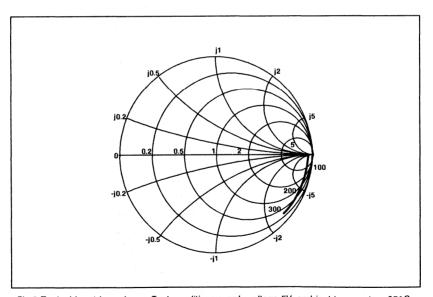

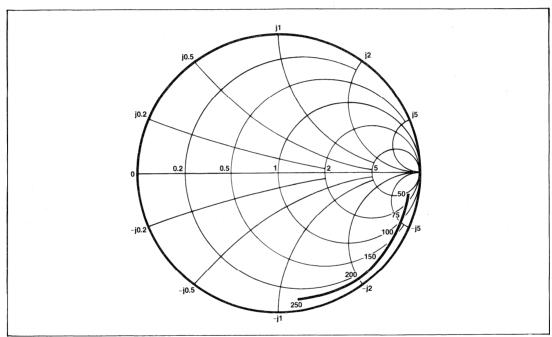

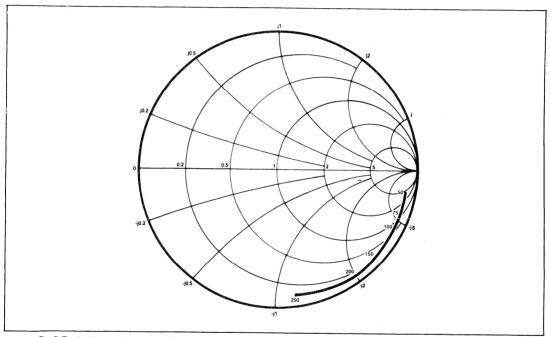

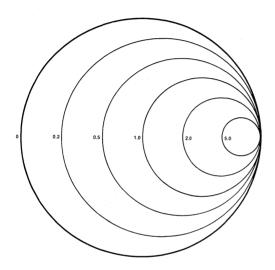

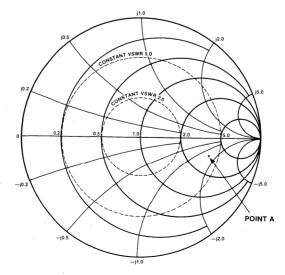

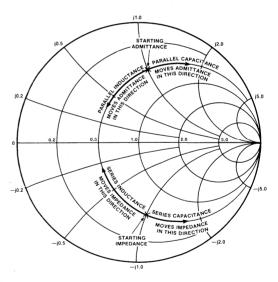

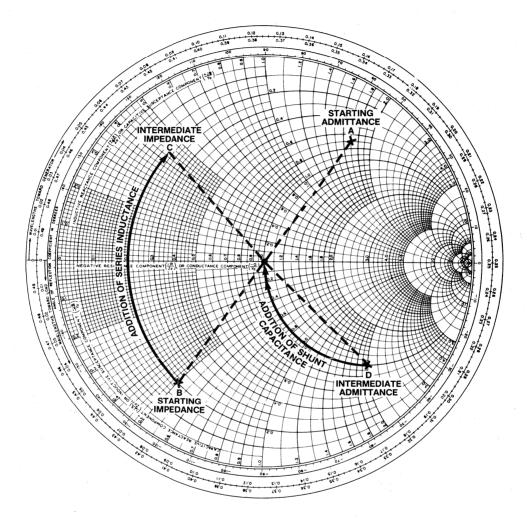

Fig. 7 Input impedance of SL6140 (50Ω normalised)

# SL6270C GAIN CONTROLLED MICROPHONE PREAMPLIFIER/VOGAD

The SL6270 is a silicon integrated circuit combining the functions of audio amplifier and voice operated gain adjusting device (VOGAD).

It is designed to accept signals from a low sensitivity microphone and to provide an essentially constant output signal for a 50dB range of input. The dynamic range, attack and decay times are controlled by external components.

# **FEATURES**

- Constant Output Signal

- Fast Attack

- Low Power Consumption

- Simple Circuitry

## **APPLICATIONS**

- Audio AGC Systems

- Transmitter Overmodulation Protection

- Tape Recorders

# QUICK REFERENCE DATA

Supply Voltage: 4.5V to 10V Voltage Gain: 52dB

## **ABSOLUTE MAXIMUM RATINGS**

Supply voltage: 12V

Storage temperature : -55°C to +125°C

Fig.1 Pin connections, SL6270 - CM (bottom view)

Fig.2 Pin connectons, SL6270 - DP (top view)

Fig.3 SL6270 block diagram

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

Supply voltage Vcc: 6V

Input signal frequency: 1kHz

Ambient temperature: -30°C to +85°C

Test circuit shown in Fig. 4

| Characteristic                 |      | Value |      |        | O dial                                |  |  |

|--------------------------------|------|-------|------|--------|---------------------------------------|--|--|

| Characteristic                 | Min. | Тур.  | Max. | Units  | Conditions                            |  |  |

| Supply current                 |      | 5     | 10   | mA     |                                       |  |  |

| Input impedance                | 1    | 150   |      | Ω      | Pin 4 or 5                            |  |  |

| Differential input impedance   | 1    | 300   |      | Ω      |                                       |  |  |

| Voltage gain                   | 40   | 52    | i    | dB     | 72μV rms input pin 4                  |  |  |

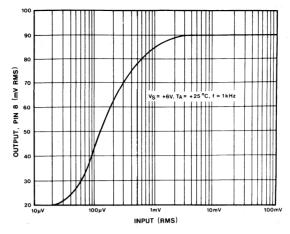

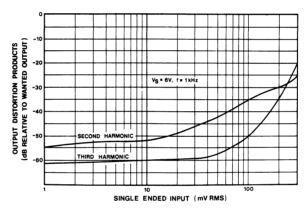

| Output level                   | 55   | 90    | 140  | mV rms | 4mV rms input pin 4                   |  |  |

| THD                            | ł    | 2     | 5    | %      | 90mV rms input pin 4                  |  |  |

| Equivalent noise input voltage |      | 1     |      | μ٧     | 300Ω source, 400Hz to 25kHz bandwidth |  |  |

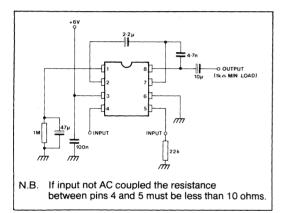

Fig.4 SL6270 test and application circuit

Fig.5 SL6270 frequency response

# **APPLICATION NOTES**

# Voltage gain

The input to the SL6270 may be single ended or differential but must be capacitor coupled. In the single-ended mode the signal can be applied to either input, the remaining input being decoupled to ground. Input signals of less than a few hundred microvolts rims are amplified normally but as the input level is increased the AGC begins to take effect and the output is held almost constant at 90mV rms over an input range of 50dB.

The dynamic range and sensitivity can be reduced by reducing the main amplifier voltage gain. The connection of a 1k resistor between pins 7 and 8 will reduce both by approximately 20dB. Values less than  $680\Omega$  are not advised.

Frequency response

The low frequency response of the SL6270 is determined by the input, output and coupling capacitors. Normally the coupling capacitor between pins 2 and 7 is chosen to give a -3dB point at 300Hz, corresponding to  $2.2\mu F$ , and the other capacitors are chosen to give a response to 100Hz or less.

The SL6270 has an open loop upper frequency response of a few MHz and a capacitor should be connected between pins 7 and 8 to give the required bandwidth.

# Attack and delay times

Normally the SL6270 is required to respond quickly by holding the output level almost constant as the input is increased. This 'attack time', the time taken for the output to return to within 10% of the original level following a 20dB increase in input level, will be approximately 20ms with the circuit of Fig.4. It is determined by the value of the capacitor connected between pin 1 and ground and can be calculated approximately from the formula:

Attack time =  $0.4 \text{ms}/\mu\text{F}$

The decay time is determined by the discharge rate of the capacitor and the recommended circuit gives a decay rate of 20dB/second. Other values of resistance between pin 1 and ground can be used to obtain different results.

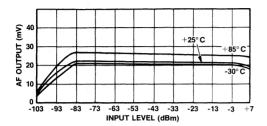

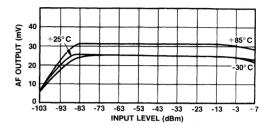

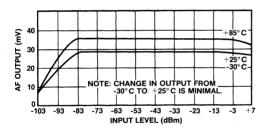

Fig. 6 Voltage gain (single ended input) (typical)

Fig. 7 Overload characteristics (typical)

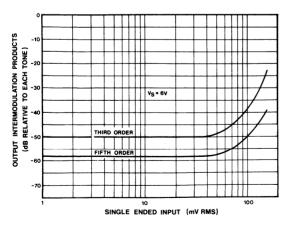

Fig. 8 Typical Intermodulation distortion (1.55 and 1.85kHz tones)

Fig. 9 Open loop frequency response (typical)

# **SL6310C**

# 500mW SWITCHABLE AUDIO AMPLIFIER/OP AMP

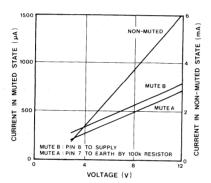

The SL6310C is a low power audio amplifier which can be switched off by applying a mute signal to the appropriate pin. Despite the low quiescent current consumption of 5mA (only 0.6mA when muted) a minimum output power of 400mW is available into an  $8\Omega$  load from a 9V supply.

# **FEATURES**

- Can be Muted with High or Low State Inputs

- Operational Amplifier Configuration

- Works Over Wide Voltage Range

# **APPLICATIONS**

- Audio Amplifier for Portable Receivers

- Power Op. Amp

- High Level Active Filter

# **QUICK REFERENCE DATA**

Supply Voltage: 4.5V to 13.6V

Voltage Gain: 70dB

Output into  $8\Omega$  on 9V Supply: 400 mW (min.)

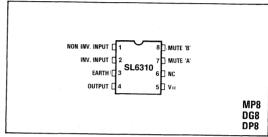

Fig.1 Pin connections SL6310 - (top view)

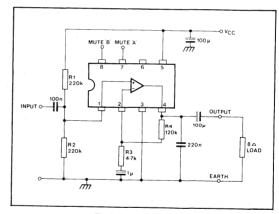

Fig.2 SL6310 test circuit

# **ABSOLUTE MAXIMUM RATINGS**

Supply voltage: 15V

Storage temperature: -55°C to +125°C

# **ELECTRICAL CHARACTERISTICS**

# Test conditions (unless otherwise stated):

Supply voltage Vcc: 9V

Ambient temperature: -30°C to +85°C

Mute facility: Pins 7 and 8 open circuit frequency = 1kHz

| Ohamaataniati'a                                                                                            |           | Value                         |                              |                            | Candidiana                                                                                         |

|------------------------------------------------------------------------------------------------------------|-----------|-------------------------------|------------------------------|----------------------------|----------------------------------------------------------------------------------------------------|

| Characteristic                                                                                             | Min.      | Тур.                          | Max.                         | Units                      | Conditions                                                                                         |

| Supply current Supply current muted (A) Supply current muted (B) Input offset voltage Input offset current |           | 5.0<br>0.55<br>0.6<br>2<br>50 | 7.5<br>1<br>0.9<br>20<br>500 | mA<br>mA<br>mA<br>mV<br>nA | Pin 7 via 470k to earth<br>Pin 8 = Vcc<br>Rs ≤ 10k                                                 |

| Input bias current (Note 1)<br>Voltage gain<br>Input voltage range                                         | 40        | 0.2<br>70<br>2.1<br>10.6      | 1                            | μA<br>dB<br>V<br>V         | Vcc = 4.5V<br>Vcc = 13V                                                                            |

| CMRR<br>Output power<br>THD                                                                                | 40<br>400 | 60<br>500<br>0.4              | 3                            | dB<br>mW<br>%              | $\begin{array}{l} Rs \leqslant 10k \\ R_L = 8\Omega \\ Pout = 400 mW, \\ Gain = 28 dB \end{array}$ |

### NOTE

<sup>1.</sup> The input bias current flows out of pins 1 and 2 due to PNP input stage

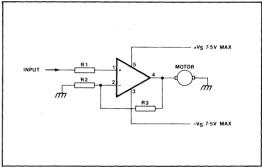

Fig.3 SL6310 lamp driver

Fig.4 SL6310 servo amplifier

## **OPERATING NOTES**

### Mute facility

The SL6310 has twomute control pins to allow easy interfacing to inputs of high or low levels. Mute control 'A', pin 7, is left open circuit or connected to a voltage within 0.65 volt of Vcc (via a  $100k\Omega$  resistor) for normal operation. When the voltage on pin 7 is reduced to within 1 volt of earth (via a  $100k\Omega$  resistor) the SL6310 is muted.

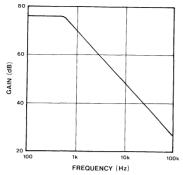

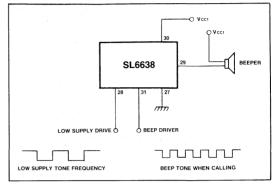

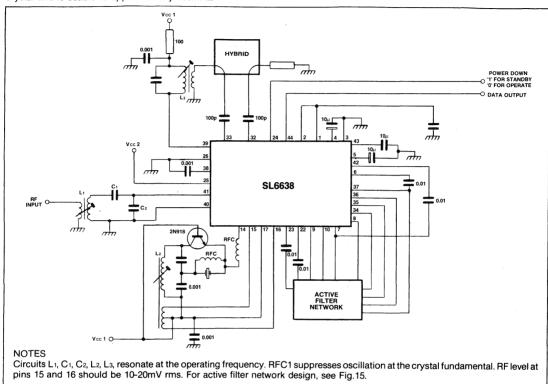

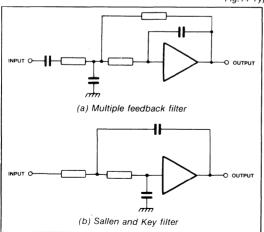

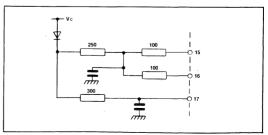

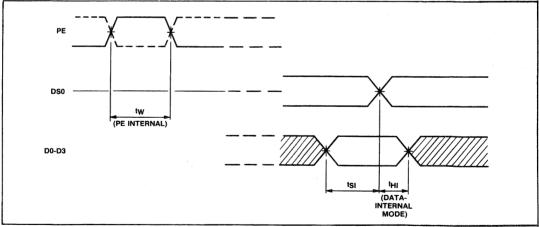

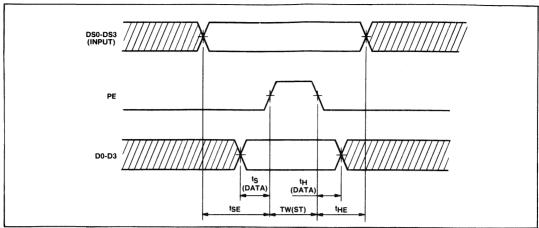

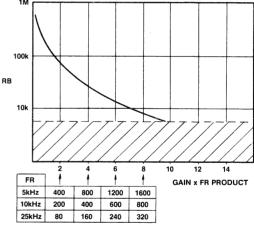

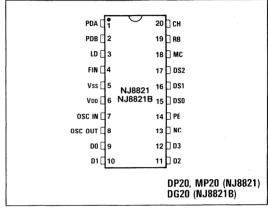

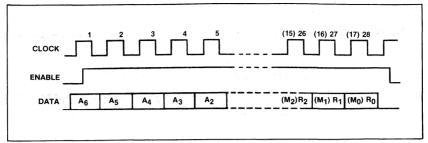

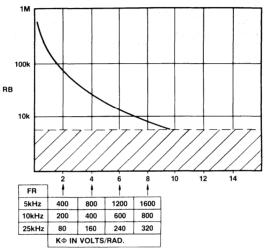

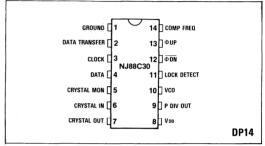

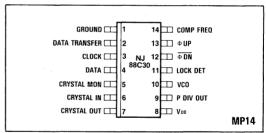

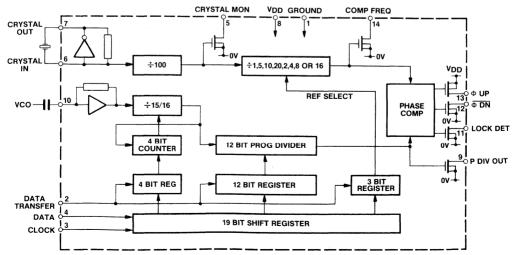

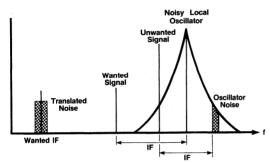

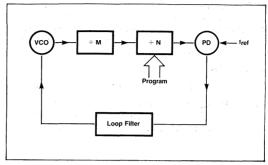

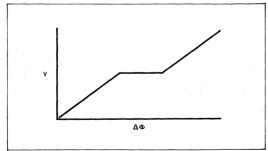

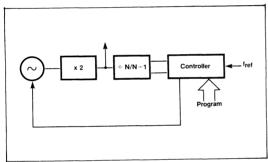

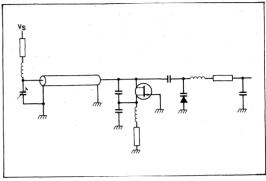

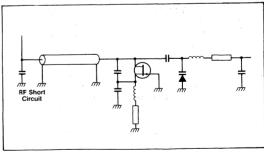

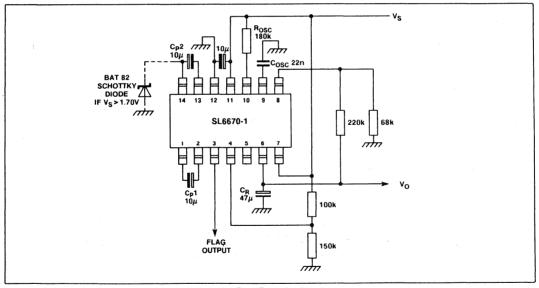

## Audio amplifier